6層+Pad on Viaの基板作成をしました。

KiCadで回路図・アートワークを作成をしています。

実際にパッドオンビアの基板発注した内容を紹介します。

Pad on ViaをKiCadで設計して、PCBWayで基板作成してみた

6層+Pad on Viaの基板作成をしました。

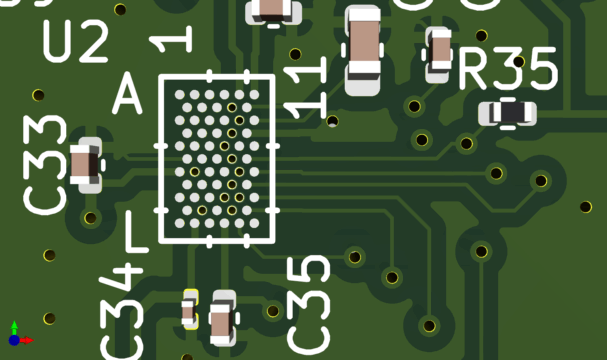

高密度の0.4mmピッチのWLCSP(BGA)パッケージのAudio_ICを搭載するためです。

KiCadで回路図・アートワークを作成をしています。

実際にパッドオンビアの基板発注した内容まで紹介します。

オープンソースカンファレンス2025 Hokkaidoでこの内容を報告しました。

下記がまとめた発表スライドです。よろしければ一緒にご覧ください。

ブログ記事としてもアップしています。

オープンソースカンファレンス2025 HokkaidoでLT発表してきた

BLE Audio Design Challenge

今回の基板は海外のコンテスト(BLE Audio Design Challenge)の一環で作成しました。

Bluetooth LE Audioのプロジェクトを開発するコンペでした。

詳細は下記公式ページを参照ください。

筆者のプロジェクトページは下記となります。基板概要からテストした内容を紹介しています。

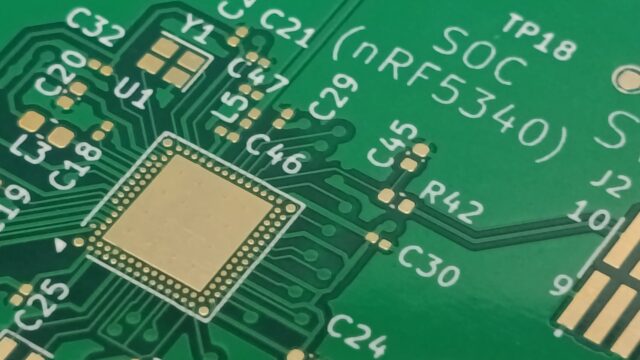

SOCとAudio ICが0.4mmピッチ

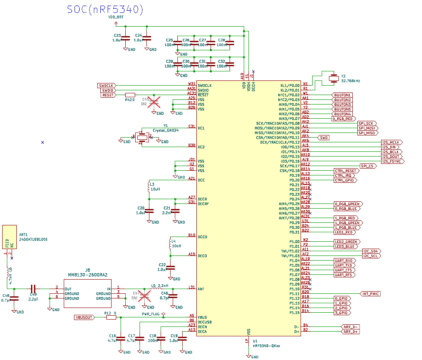

コンテストで使うICが指定されていました。

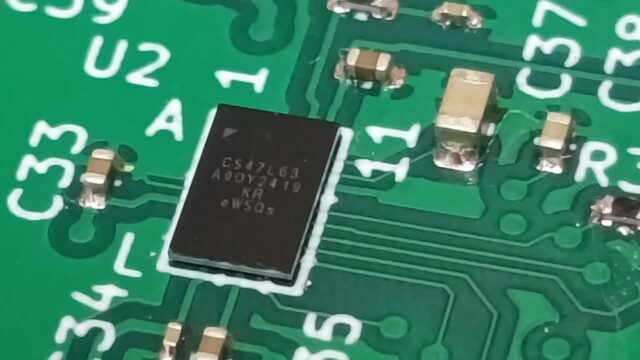

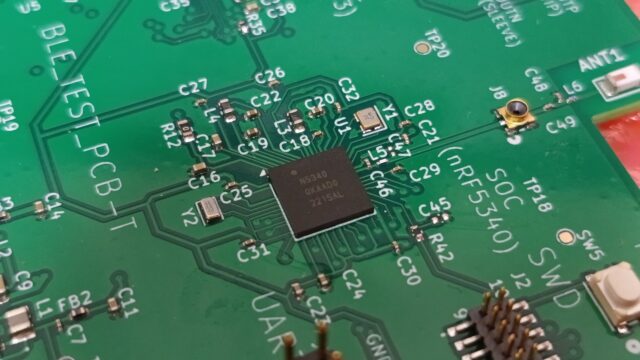

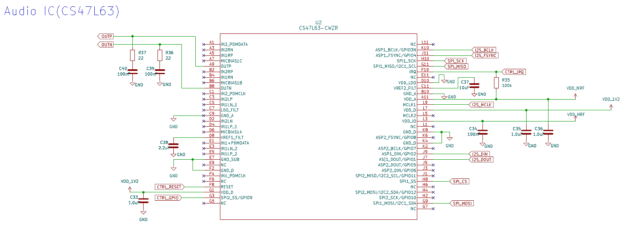

「SOCのnRF5340」と「Audio_ICのCS47L63」が0.4㎜ピッチのWLCSP(BGA)です。

単純には内側のピンに配線できないICです。

(表層で配線しようとすると、周りのピン・配線に干渉してしまいます)

回路図・アートワーク

実際のKiCadのデータに関しては、下記GitHubに保存しています。

パターン専門の設計者でなく、また趣味で作ったものですが、動作確認は出来ています。

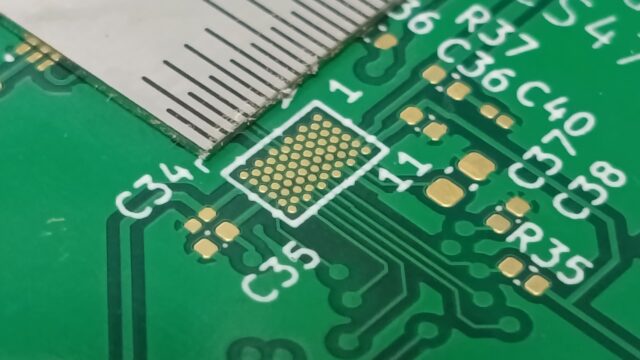

Pad On Via (Via in Pad)

そのため、今回はPad on Via(Via in Pad)という手法を使っています。

本来ビアの上にはパッドは引けませんが、ビアを樹脂で埋めてパッドを引く手法です。

詳細は下記のPCBWayのページをご参照ください。

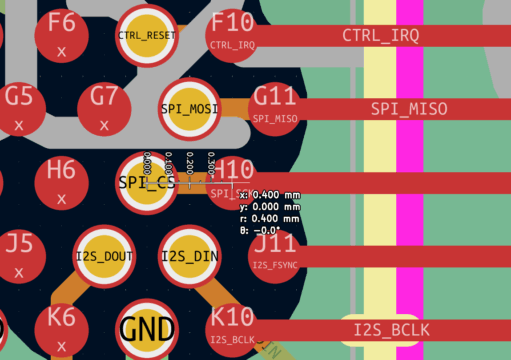

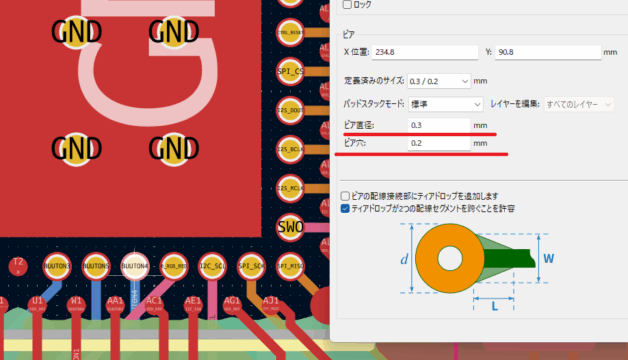

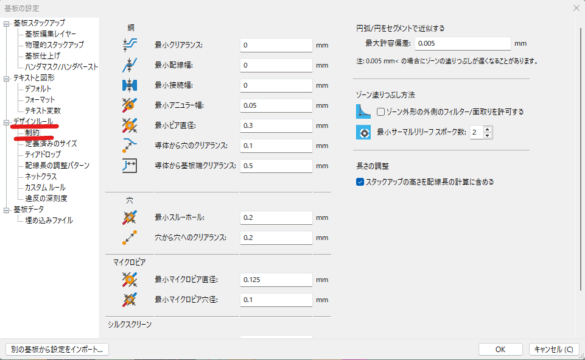

SOCとAudio_ICのデータシートのパッドサイズ確認すると下記条件です。

- SOCの1ピンの推奨パッド… φ0.2㎜(Typ)

- Audio_ICの1ピンの推奨パッド… φ0.27mm(Typ)

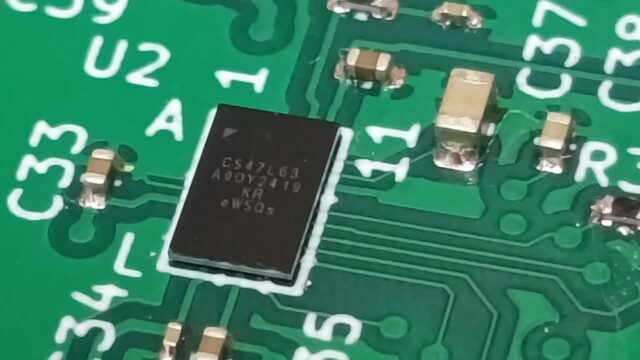

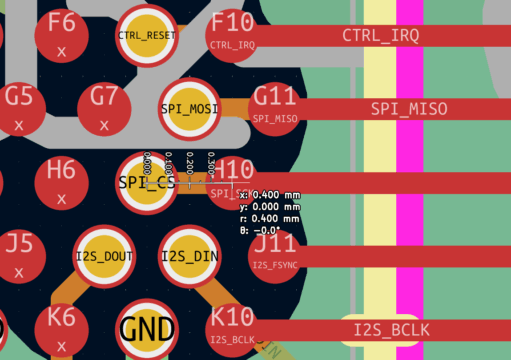

そのため、ビア穴0.2㎜、ビア直径0.3㎜としました。

この基板でパッドオンビアにした箇所は全てこの設定にしています。

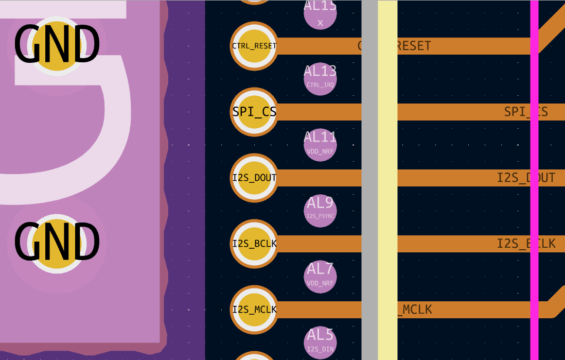

下記SOCの例だと、内側のピンを直下のビアの3層(オレンジ)から配線しています。

(他の箇所では直下のVIAから5層、6層に接続しているケースもあります。)

Audio_ICも同様に内側のピンは直下のVIAから3層に引き出しています。

(一番外側は1層目からパターンを引き出しています)

DRC(デザインルールチェック)の際にはワーニングが発生しています。

「ドリル穴と他の穴が近すぎる」です。

下記が筆者の制約条件ですが、一例です。基板条件で異なってきます。

制約条件を緩めるか、問題ない場合は無視してガーバ出力をします。

本来はしっかりルール設定すべきですが、趣味の案件のため結構雑にやっています。

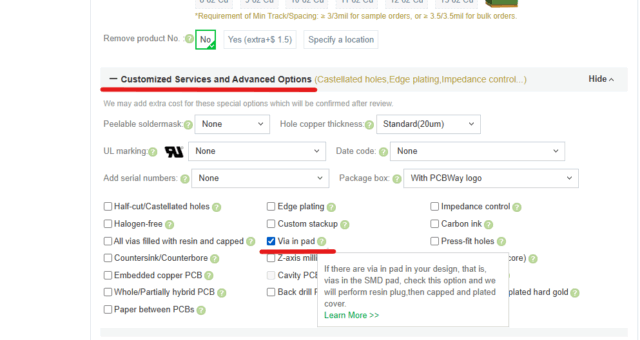

基板メーカ(PCBWay)へのパッドオンビアの伝え方

今回は基板メーカはPCBWayを利用しています。

PCBWayでは基板見積する際にオプション項目で、パッドオンビアの項目があります。

そこにチェックをいれます。

パッドオンビア箇所

・コメント箇所でどこの箇所、どのビアがパッドオンビアなのかを伝えておきます。

今回ドリル径が0.2mm+パッド径が0.3㎜の箇所を指定しています。

We have via-in-pad on the pads for U1 and U2. The via drill diameter is 0.2mm, and the pad diameter is 0.3mm.

表面処理

またパッドオンビアを使う0.2㎜/0.3mmのBGAサイズだと、表面処理も限定されます。

筆者の場合は下記で対応しました。この辺りは基板メーカと相談した方が良いです。

ENIG (Electroless Nickel Immersion Gold) with a gold thickness of 1u" for the surface finish

樹脂穴埋め

またパッドオンビア箇所はビアを樹脂穴埋めして開ける必要があります。

今回はパッドオンビア以外の箇所含めて、Resin filling(樹脂穴埋め)で対応しました。

Resin filling for all vias on the board.

*基板品質などを考慮して、パッドオンビア箇所のみ樹脂穴埋めするケースもあります。

ただ見積時に伝えれなくとも、基板発注後にENGINEERING QUERIES SHEET(通称EQ)が来ます。

基板業者からの質問について回答します。

パッドオンビアは必要な時だけ

可能ならなるべく、パッドオンビアを使わない方が良いです。

特に趣味では、コストと納期が一気に跳ね上がるため、作成者にダメージ大です。

(今回はコンテストで指定のICだったため、強制的に使った理由があります)

納期

普通の趣味の2層基板だと1日~2日で基板生板が作成されます。

ただ今回の6層+Pad On Viaだと12~13日かかりました。相当納期が長くなります。

実装や配送を含めると≒1か月かかりました。

- 基板(生板)製造: 約12-13日

- 基板組み立て: 約2週間

- 配送: 約5日

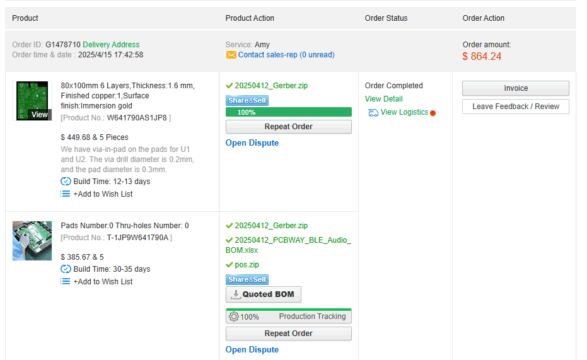

コスト

よくある趣味の2層基板だと5枚で≒$5程度で作成できると思います。

ただ今回の6層+Pad On Viaは5枚で≒$450でした。約90倍の価格となります。

(実装費用・部品代含めると≒$860でした)

実際のパッドオンビア基板

今回は実装した基板5枚以外にも生板1枚もいただきました。

全部のビアを樹脂穴埋めしたので、VIAが基本隠れています。

(導通確認とかでVIAを使用する方は注意が必要です。)

Audio_ICが表層だけではパターン引けないICと分かります。

外側のピンは表層で引けますが、内側のピンはPad On Viaでないと無理です。

SOCも同様です。外側使っている内側のピンはPad On Viaで接続しています。

まとめ

6層+Pad on Viaの基板作成をしました。

KiCadで回路図・アートワークを作成をしています。

実際にパッドオンビアの基板発注した内容を紹介しました。

今回の記事はBluetooth LE Audioコンペに参加していた内容の一環です。

BLE Audio Design Challengeというコンテストです。下記でまとめ記事を紹介しています。

BLE Audio Design Challengeの実装コンペに参加した件

コメント