FPGA

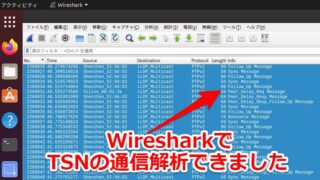

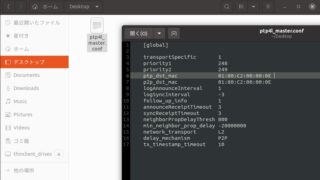

FPGA TSNの時刻同期の仕組み。IEEE 802.1QBVを試してみた

TSNの時刻同期の仕組みの重要なポイントである、IEEE 802.1QBVを試してみました。通信トラフィックをスケジューリングする仕様を確認しています。実際の通信テストから解析方法まで紹介します。

FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  AI

AI  AI

AI  AI

AI  AI

AI  AI

AI  FPGA

FPGA  AI

AI  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA