XilinxのTSNのIPを部分的に確認してみました。基本的には個人では使用できないIPです。

評価ボードのデザインファイルから一部参照することが可能です。

確認する手順を紹介します。

TSNのXilinxのIPを部分的に確認してみた

XilinxのTSN(Time Sensitive Networking)のIPを部分的に確認してみました。

基本的には個人では使用できないIPです。

ダウンロードするには販売代理店のエンジニアの確認が必要になるためです。

ただし、KR260のハードウェアデザインからTSNのIPを部分的に確認できます。

KR260は実際にTSNをテストできるXilinxのFPGAボードです。

ダウンロードから確認方法までの流れを紹介します。

TSNとKR260について

TSNとKR260については、今までに下記記事で使い方をまとめています。

もし興味ある方はご一緒にご確認ください。

TSNの通信テストと環境構築に関しては下記記事で実施・紹介しています。

TSN Ethernetの実装をFPGA(KR260)で試してみた

TSNスイッチ、またマスター・スレーブとして設定を確認しています。

TSNスイッチとして使えるFPGAの評価ボード(KR260)

テストしたPTP通信がTSNに対応しているかの確認を下記記事で紹介しています。

TSNとPTPの違いは?通信テストの設定・ログから確認してみた

テスト環境は「PTP対応のLANカード(NIC)」と「TSNに対応のFPGAボード」です。

PTP対応のLANカード(NIC)の詳細については下記記事で紹介しています。

IEEE-1588/PTP対応のLANカード(NIC)を動かしてみた

またTSNに対応のFPGAボード(KR260)に関しては下記記事で紹介しています。

Xilinxの公式のIP・ハードウェアデザイン

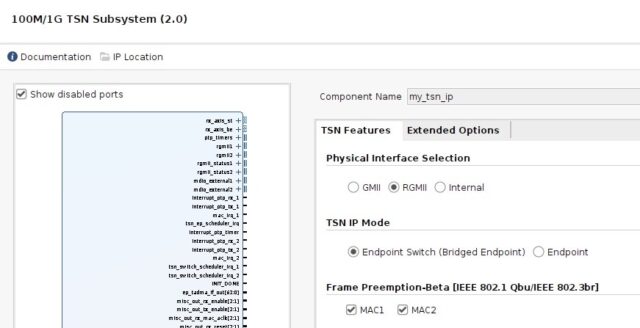

XilinxのTSNのIPは「100M/1G TSN Subsystem」という名称です。

https://japan.xilinx.com/products/intellectual-property/1gtsn.html

※ダウンロードするにはXilinxの販売代理店のエンジニアの確認が必要です。

KR260のハードウェアデザインを参照する手順は、下記ドキュメントを参照しています。

https://xilinx.github.io/kria-apps-docs/kr260/build/html/docs/build_vivado_design.html

同様に実施する方はご確認お願いします。

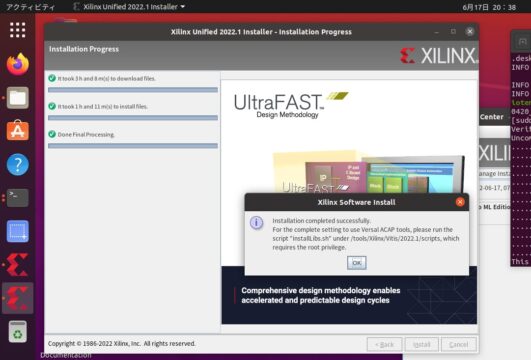

Vivado(Vitis)をインストールする

XilinxのFPGAのIPを確認するには、専用のソフトを使用する必要があります。

Vivado・Vitisを用意します。まとめてインストールできます。

筆者の環境はLinuxのデスクトップPCで実施しています。

公式ページからインストーラーをダウンロードして、実行します。

https://japan.xilinx.com/support/download/index.html/content/xilinx/ja/downloadNav/vitis.html

下記のライブラリは最低限インストールはしておいた方が良いです。

|

1 2 3 4 5 6 7 |

sudo apt update sudo apt upgrade sudo apt install libncurses5 sudo apt install libtinfo5 sudo apt install libncurses5-dev libncursesw5-dev sudo apt install ncurses-compat-libs sudo apt install ocl-icd-libopencl1 opencl-headers ocl-icd-opencl-dev git |

Vitisがインストールのデフォルトだとroot/toolsに作られます。

インストールしたい箇所にフォルダ作って、権限を付けてインストールしておきます

|

1 2 3 |

cd / sudo mkdir tools sudo chmod 777 tools |

KR260のハードウェアデザインを入手する

KR260のハードウェアデザインは誰でもダウンロード可能です。

Linuxの環境でgitcloneできます。

KR260含めた、KRIAというプラットフォーム環境を入手できました。

|

1 |

git clone --recursive https://github.com/Xilinx/kria-vitis-platforms.git |

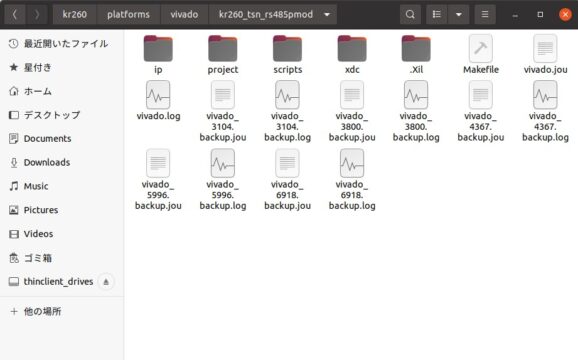

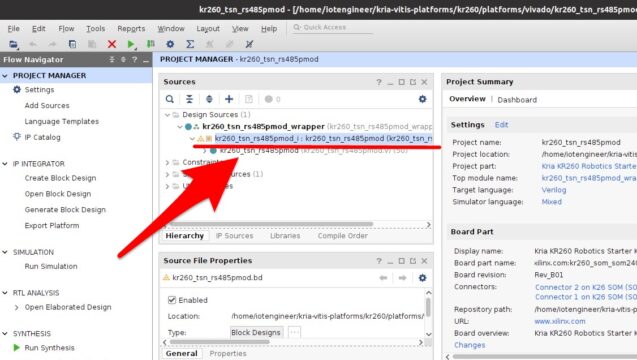

TSN通信するサンプルデモのデザインも含まれています。

「kr260_tsn_rs485pmod」という名称です。

「kria-vitis-platforms/kr260/platforms/vivado/kr260_tsn_rs485pmod」でmakeします

|

1 2 |

cd ~/kria-vitis-platforms/kr260/platforms/vivado/kr260_tsn_rs485pmod make xsa |

起動に関してはvivadoのセッティングのスクリプトを起動して、立ち上げるだけです。

|

1 2 3 4 |

source ~/Vivado/2022.1/.settings64-Vivado.sh source ~/Vitis/2022.1/.settings64-Vitis.sh vivado |

makeするに32GBのメモリが必要だった

makeするのに注意点があります。それなりのスペックを持ったPCが必要です。

筆者のLinuxのデスクトップPCはメモリ16GBです。

それでもOut of memoryが出ました。(メモリ不足のエラー)

メモリが16GBでは足りなかったので、メモリスワップの容量を16GB増やしました。

|

1 2 3 |

sudo dd if=/dev/zero of=/var/swap bs=1M count=16384 sudo mkswap /var/swap sudo swapon /var/swap |

再ビルドにはTSNのIPが必要

一応makeしてTSNを使ったデザインを復元できるのですが、完全ではありません。

エラーが出ています。TSN関連のIPが無い旨の内容です。

|

1 2 3 4 |

[Common 17-69] Command failed: This design contains one or more cells for which bitstream generation is not permitted: kr260_tsn_rs485pmod_i/ta_dma_0/inst (<encrypted cellview>) kr260_tsn_rs485pmod_i/my_tsn_ip/inst/tsn_endpoint_block_0/inst/TSN_TOP (<encrypted cellview>) If a new IP Core license was added, in order for the new license to be picked up, the current netlist needs to be updated by resetting and re-generating the IP output products before bitstream generation. |

サンプルデザインを見るぐらいは可能

一応makeしたプロジェクトを開けばデザインは確認できます。

(先述しましたがTSNのIPが入手できないので、本当に表面上だけの確認になりますが…)

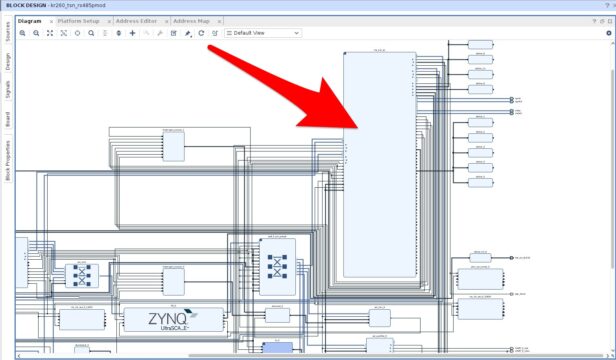

実際にKR260のTSN通信のサンプルデモを開くと、TSNのIP箇所も確認できます。

(接続量を見ると、個人で一から配線できるレベルではなさそうです…)

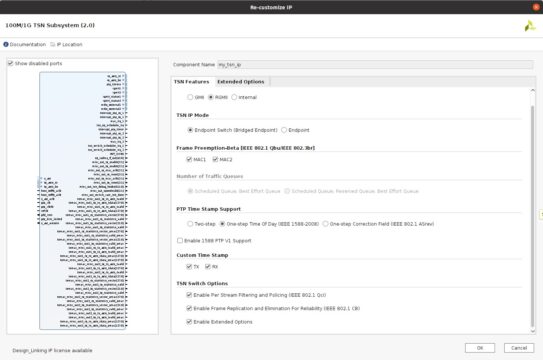

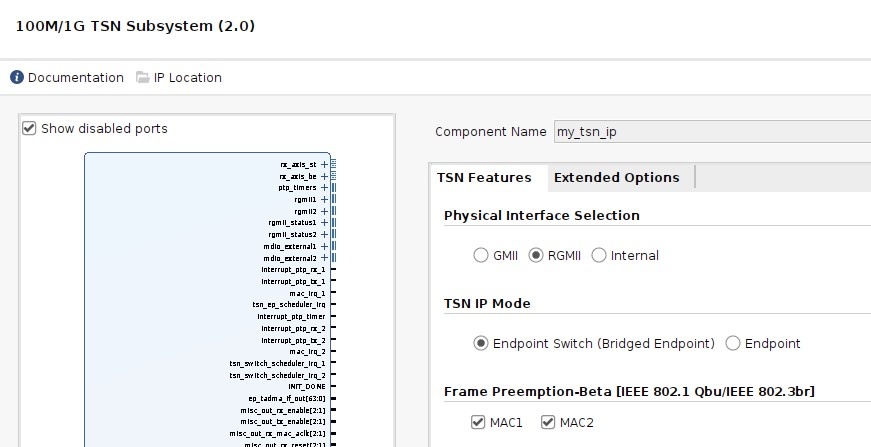

ただ中身まで見ると、基本的なIPの機能は確認できます。

「物理的なIF…RGMII」「TSNのIPのモード…Endpoint Switch」などがあります。

(基本的な内容程度ならば確認できそうです)

まとめ

XilinxのTSNのIPを部分的に確認してみました。基本的には個人では使用できないIPです。

(早く一般公開してほしいIPです)

但し、評価ボードのデザインファイルから一部参照することが可能です。

よろしければ皆さまも、TSNのIPが気になりましたら試してみて下さい。

下記記事にて、筆者個人でTSN通信テストした内容をまとめています。

よろしければ一緒にご覧ください。(リンク先はこちら)

コメント