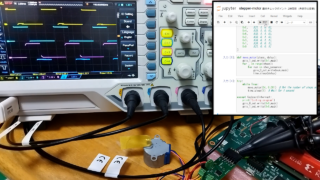

FPGA

FPGA VivadoやVitis 2025でKV260やKR260を使う際の注意点

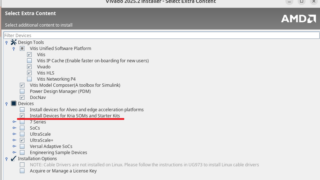

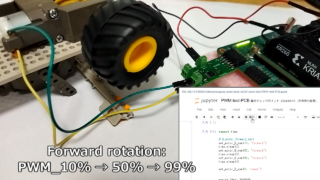

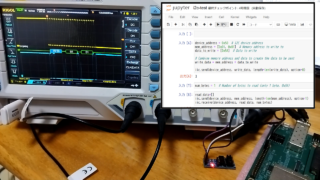

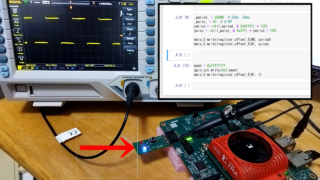

VivadoやVitis 2025.2をインストールしてみました。ただkria(KV260やKR260)のボードを使う場合に注意点があります。最初のセットアップ時にkriaのボード設定もインストールをおススメします。VivadoやVitis...

FPGA

FPGA  エンジニア

エンジニア  AI

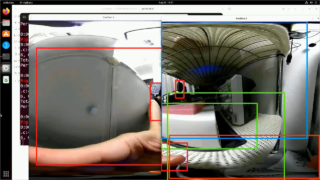

AI  AI

AI  AI

AI  AI

AI  AI

AI  AI

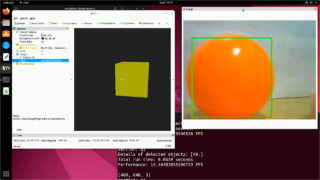

AI  AI

AI  AI

AI  AI

AI  AI

AI  AI

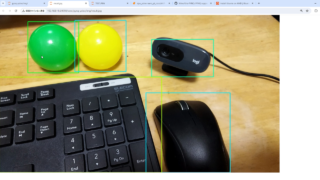

AI  AI

AI  AI

AI  AI

AI  AI

AI  AI

AI  エンジニア

エンジニア  FPGA

FPGA  FPGA

FPGA  FPGA

FPGA  AI

AI  FPGA

FPGA  FPGA

FPGA  AI

AI  AI

AI  AI

AI  AI

AI  AI

AI