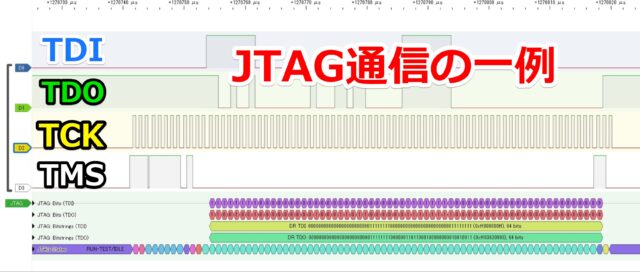

JTAG通信の波形をロジックアナライザで解析してみました。

TMS信号からのステートの状態遷移含めて確認しています。

JTAGが未接続・アイドル・書き込みの際に、どのような波形になるかを紹介します。

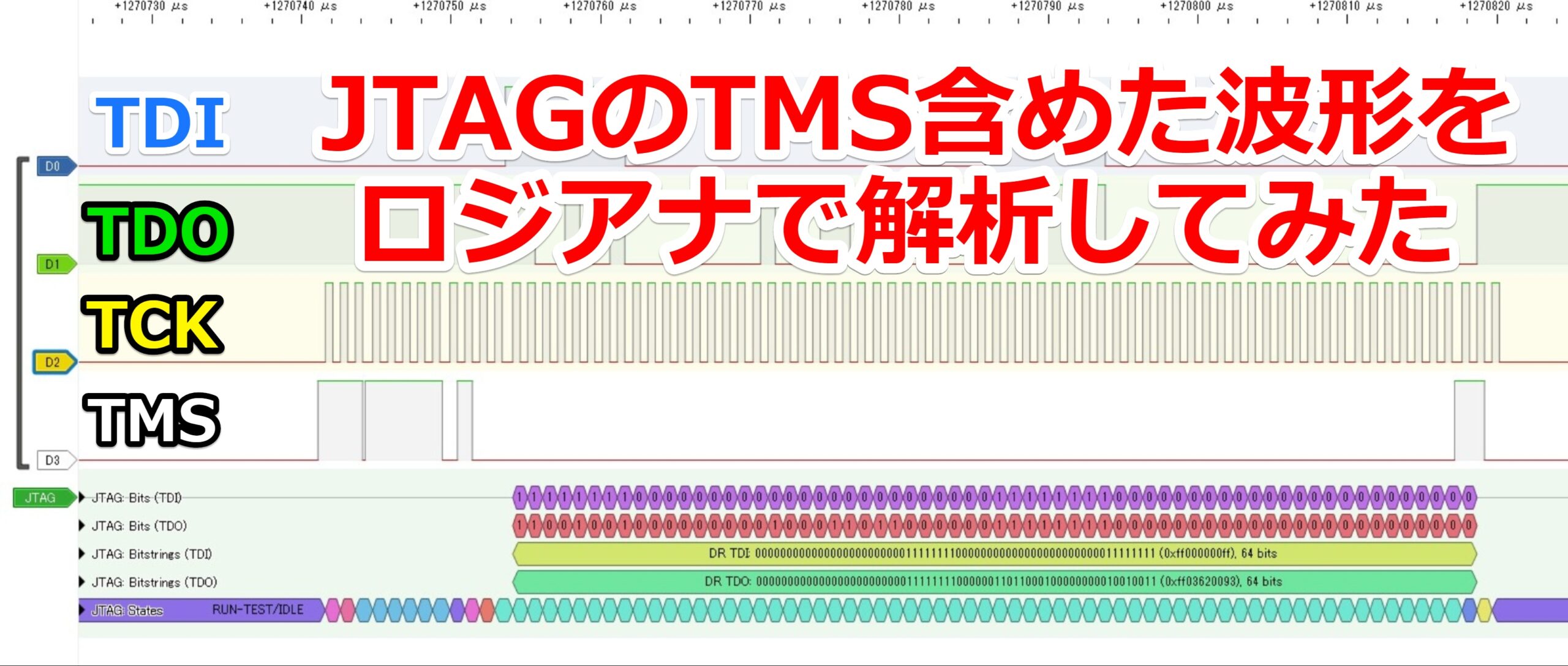

JTAGのTMS含めた波形をロジアナで解析してみた

JTAG通信をロジアナで解析してみました。

JTAGの信号であるTDI,TDO,TCK,TMSの波形を測定しています。

TMSはJTAGデバイスのコントローラ(TAPコントローラ)の状態遷移に使われます。

※TMS…Test Mode Select

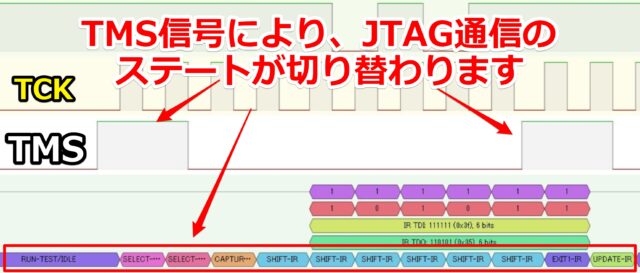

TMS信号により、JTAG通信のステートが切り替わります。

「未接続」「アイドル(通信中)」「書き込み」のJTAG通信を確認しました。

テストした環境から、解析したJTAG信号・ステートの状態まで詳細に紹介していきます。

実際にJTAG通信をロジアナで測定した動画も紹介しています。

信号解析できている様子が分かりますので、是非合わせてご覧ください。

JTAGのコネクタから信号を取り出す

JTAGは基本的にTDI,TDO,TCK,TMSの4本の信号で通信します。

ロジアナで解析するためにも、JTAGコネクタから信号を取り出します

※他にもオプションの信号もありますが、ここでは省略します。

- TDI…Test Data In

- TDO…Test Data Out

- TCK…Test Clock

- TMS…Test Mode Select

XilinxのJTAGケーブルを使います

JTAG-HS2とはXilinxのFPGAにプログラムを書き込むためのツールです。

Xilinxの評価ボードメーカとしても有名なDiligent製のケーブルとなります。

パソコンで書いたプログラムをUSB経由で簡単にFPGAに転送することが可能です。

今回使用したケーブルに関しては下記記事で詳細に紹介しています。

XilinxをJTAG-USBケーブルで書き込み!JTAG-HS2を試してみた

JTAGでFPGAに書き込みする

FPGAとJTAGケーブルの通信をロジアナで解析します。

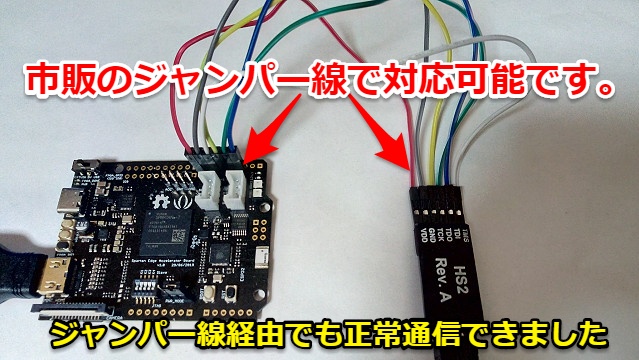

JTAGケーブルを使う上での注意点ですがピン配置は確認しましょう。

今回のテストでも「FPGA評価ボード」と「JTAGケーブル」のピン配置が異なっていました。

今回使用したFPGAの評価ボードに関しては下記記事で紹介しています。

XilinxのFPGAの評価ボードを購入してみた。Spartan7に入門!

必要に応じてジャンパーで接続して対応します。

市販の電子工作セットに入っているジャンパーでも通信できました

ロジックアナライザでJTAGを解析する

ロジックアナライザ(ロジアナ)でJTAGを解析していきます。

ロジアナの端子にJTAGの信号線4本とGNDを接続しています。

ロジアナの使い方に関しては下記記事で紹介しています。(リンク先はこちら)

ブレッドボード経由でJTAGの信号線(TDI,TDO,TCK,TMS)をロジアナと繋げます。

JTAGの周波数を落とせばブレッドボード経由でも十分に測定可能です。

テスト時の全体像(FPGA⇔JTAGケーブル⇔ロジアナ)としては下記形です。

ジャンパーケーブルも増えるので各信号線で色分けした方が良いと思います。

JTAGの通信速度を変更する

JTAGの通信速度をデフォルト設定から変更します。

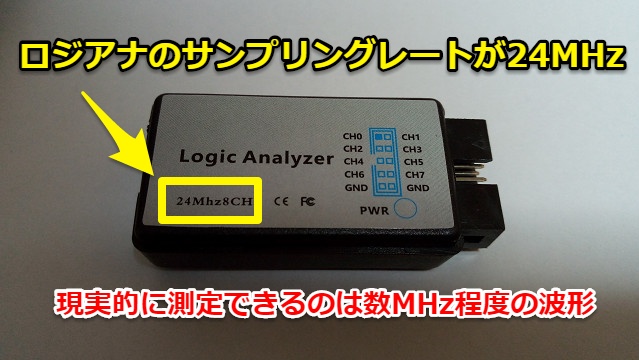

理由は今回のロジアナのサンプリングレートが最大24MHzで正確に測定出来ないためです。

現実的に波形として測定できるのは数MHz程度までとなります。

XilinxのJTAGケーブルの自動設定

最近のJTAGケーブルだとデフォルト(自動)設定で10~20MHzになるので注意が必要です。

XilinxのJTAG-HS2のデフォルト設定(AutoConnect)では10MHzになるようです。

実際に自動設定(Auto Connect)した際のログは下記形です。

JTAGのクロックのログは残っていませんでした。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 |

open_hw_manager connect_hw_server -allow_non_jtag INFO: [Labtools 27-2285] Connecting to hw_server url TCP:localhost:3121 INFO: [Labtools 27-2222] Launching hw_server... INFO: [Labtools 27-2221] Launch Output: ****** Xilinx hw_server v2020.1 **** Build date : May 27 2020 at 20:24:38 ** Copyright 1986-2020 Xilinx, Inc. All Rights Reserved. INFO: [Labtools 27-3415] Connecting to cs_server url TCP:localhost:3042 INFO: [Labtools 27-3417] Launching cs_server... INFO: [Labtools 27-2221] Launch Output: ****** Xilinx cs_server v2020.1.0 **** Build date : May 14 2020-10:10:29 ** Copyright 2017-2020 Xilinx, Inc. All Rights Reserved. connect_hw_server: Time (s): cpu = 00:00:02 ; elapsed = 00:00:10 . Memory (MB): peak = 1015.477 ; gain = 0.000 open_hw_target INFO: [Labtoolstcl 44-466] Opening hw_target localhost:3121/xilinx_tcf/Digilent/210249ADDBF6 open_hw_target: Time (s): cpu = 00:00:08 ; elapsed = 00:00:08 . Memory (MB): peak = 2193.258 ; gain = 1177.781 set_property PROGRAM.FILE {C:/Users/ioten/OneDrive/xillinx/HDMI_test/HDMI_test.runs/impl_1/HDMI_test_wrapper.bit} [get_hw_devices xc7s15_0] current_hw_device [get_hw_devices xc7s15_0] refresh_hw_device -update_hw_probes false [lindex [get_hw_devices xc7s15_0] 0] INFO: [Labtools 27-1434] Device xc7s15 (JTAG device index = 0) is programmed with a design that has no supported debug core(s) in it. |

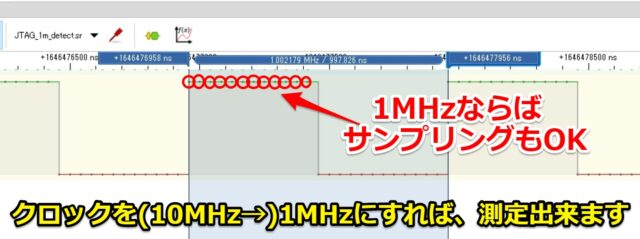

実際にJTAGのクロックを10MHzでロジアナにて確認すると、正確に測定出来ませんでした。

本来クロックとして一定の方形波になる箇所が適切にサンプリングできていません。

JTAGのクロックを変更する

JTAGのクロック(速度)を変更します。

10MHz→1MHzにすると十分にサンプリングが取れて、正確に測定出来ました。

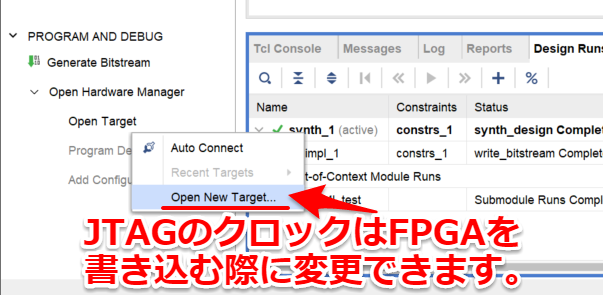

JTAGのクロックはFPGAを書き込む際の設定で変更できます。

「PROGRAM AND DEBUG」の箇所で「Open New Target」を選択します。

※普段は「Auto Connect」を選択している箇所です。

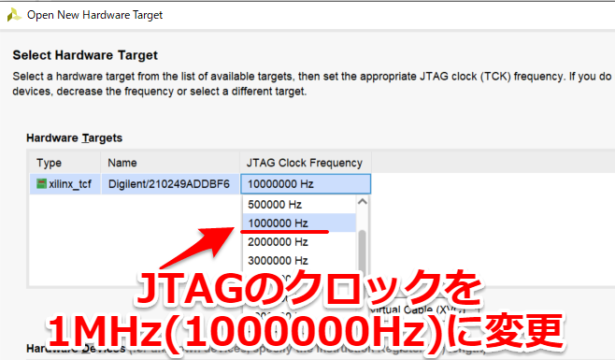

フローを進めていくと「JTAG Clock Frequency」を選択できる箇所があります。

ここで1MHz(1000000Hz)に設定しました。

1MHzに設定した際のログが下記です。

6行目辺りで周波数のパラメータが1000000に設定していることが分かります。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 |

connect_hw_server -url localhost:3121 -allow_non_jtag INFO: [Labtools 27-2285] Connecting to hw_server url TCP:localhost:3121 INFO: [Labtools 27-3415] Connecting to cs_server url TCP:localhost:3042 INFO: [Labtools 27-3414] Connected to existing cs_server. current_hw_target [get_hw_targets */xilinx_tcf/Digilent/210249ADDBF6] set_property PARAM.FREQUENCY 1000000 [get_hw_targets */xilinx_tcf/Digilent/210249ADDBF6] open_hw_target INFO: [Labtoolstcl 44-466] Opening hw_target localhost:3121/xilinx_tcf/Digilent/210249ADDBF6 set_property PROGRAM.FILE {C:/Users/ioten/OneDrive/xillinx/HDMI_test/HDMI_test.runs/impl_1/HDMI_test_wrapper.bit} [get_hw_devices xc7s15_0] current_hw_device [get_hw_devices xc7s15_0] refresh_hw_device -update_hw_probes false [lindex [get_hw_devices xc7s15_0] 0] INFO: [Labtools 27-1434] Device xc7s15 (JTAG device index = 0) is programmed with a design that has no supported debug core(s) in it. set_property PROBES.FILE {} [get_hw_devices xc7s15_0] set_property FULL_PROBES.FILE {} [get_hw_devices xc7s15_0] set_property PROGRAM.FILE {C:/Users/ioten/OneDrive/xillinx/HDMI_test/HDMI_test.runs/impl_1/HDMI_test_wrapper.bit} [get_hw_devices xc7s15_0] program_hw_devices [get_hw_devices xc7s15_0] INFO: [Labtools 27-3164] End of startup status: HIGH refresh_hw_device [lindex [get_hw_devices xc7s15_0] 0] INFO: [Labtools 27-1434] Device xc7s15 (JTAG device index = 0) is programmed with a design that has no supported debug core(s) in it. |

JTAGのプロトコルをロジアナで確認する

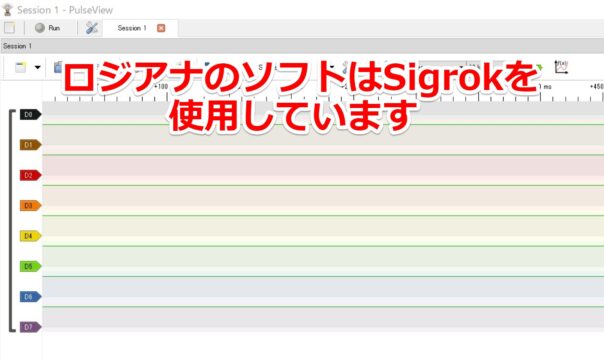

ロジアナのJTAGの設定も簡単です。ロジアナのソフトを起動します。

今回はSigrokというフリーソフトを使っています。

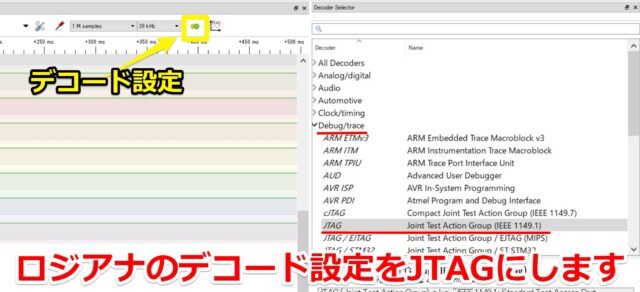

ロジアナのデコード設定をJTAGにする

Sigrokを開いたら、デコード設定のボタンをクリックします。

一覧からJTAGを選択すれば、自動的にロジアナがプロトコルを解析してくれます。

※Debug/traceの項目にJTAGがあります

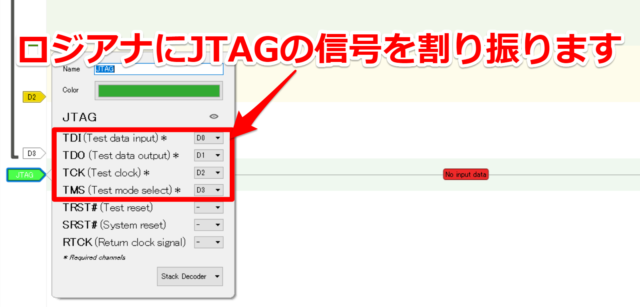

JTAGのピンアサインをロジアナに割り振ります

JTAGのデコード箇所をクリックすると、JTAGの信号を割り振ることができます。

ロジアナに接続した各JTAGの信号(TDI,TDO,TCK,TMS)を設定します。

今回はCH0_TDI、CH1_TDO、CH2_TCK、CH3_TMSとしています。

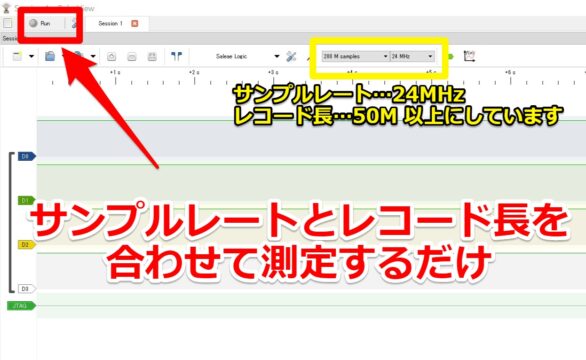

あとはサンプルレートとレコード長を合わせて測定するだけです。

サンプルレートは最大の24MHzにして、レコード長は50M samples以上を選んでいます。

冒頭でも紹介しましたが、実際にJTAG通信を解析した動画です。

未接続・接続中・書き込みの各タイミングでJTAGの波形を確認しています。

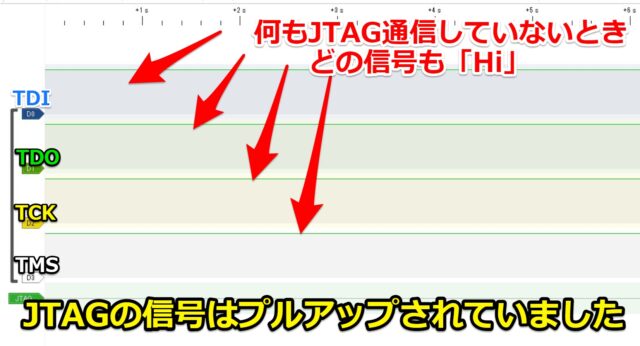

JTAG回路のプルアップを確認する

最初はFPGAを「電源ON」のみの状態で測定しました。

※JTAGケーブルには配線していますが、まだ何も設定していない状態です。

測定するとTDI,TDO,TCK,TMSの全てのJTAG信号が「Hi(1)」でした。

JTAG回路の信号はプルアップされていることが分かります。

JTAG接続した波形を確認する

FPGAにJTAG接続した状態をロジアナで測定します。

但し、プログラムは書き込んでいない(アイドル)状態です

先述したように今回はJTAGのクロックは1MHzで接続しています。

秒単位の長い時間帯域でみると下記のような波形となります。

基本的にはIDLE状態ですが、一定間隔(約65ms)で通信していました。

一定間隔で通信しているブロックを見ると、更に何個かのブロックに分かれています。

一連の塊で約1.6ms程でした。

一定間隔のブロックの先頭箇所をアップすると下記形です。

TCKを基準に、他TDI,TDO,TMSが動作しています。

JTAGの周波数を確認する

JTAGのクロック(周波数)であるTCKが設定した値になっていることを確認します。

TCKの周波数1MHz(周期1us)であることを測定出来ました。

JTAGのステートを確認する

全てのJTAG(TAPコントローラ)のステートは難しいですが、部分的にでも確認していきます。

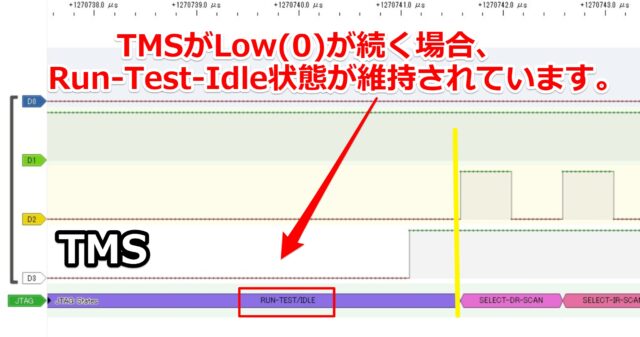

TMS信号はステートの状態遷移に使われます。

最初にTMS信号が入ってリセットがかかる箇所を中心に確認していきます。

JTAG(TAPコントローラ)のステートに関しては下記PDFを参考にさせていただきました。

Xilinx様にはこの場を借りてお礼を申し上げます。

https://japan.xilinx.com/support/documentation/application_notes/j_xapp069.pdf

Run-Test-Idle

TMSがLow(0)が続く場合、「Run-Test-Idle」のアイドル状態が維持されています。

TMSをHi(1)にすることでステートが遷移することを確認出来ました。

Test-Logic-Reset

TMSをHi(1)後に「Select-DR-Scan」「Select-IR-Scan」に移行しています。

その後「Test-Logic-Reset」のステートに遷移してリセットをしています。

(仕様通りに)TCKの5回分、TMSがHi(1)を維持していることを確認できました。

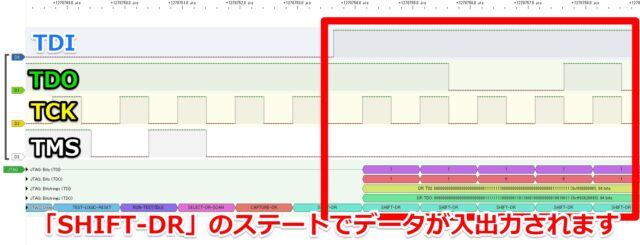

SHIFR-DR

リセットが終わった後は、再度TMSが動きます。

「Run-Test-Idle」「Select-DR-Scan」「Capture-DR」の順でステートが遷移しています。

そして「SHIFT-DR」でTMSはLow(0)を維持して、データが入出力されています。

他にも多くのステート・状態遷移があります。(全16ステート)

今回紹介したのはあくまで、ほんの一部であることをご了承下さい。

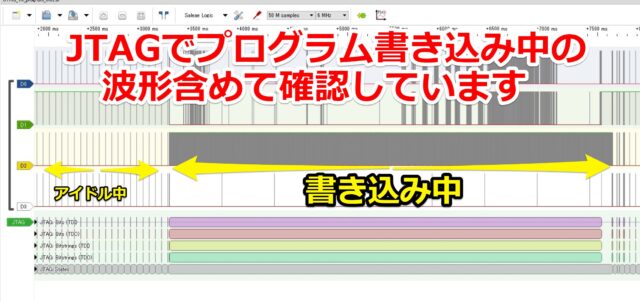

JTAG書き込み中の波形を確認する

FPGAにプログラムを書き込んでいる際にJTAGの波形を確認します。

Xilinxの開発環境(Vivado)からプログラムします。

書き込み前(アイドル中)は一定間隔でしかJTAG波形が確認されませんでした。

しかし、プログラム書き込み中はTCK(クロック)が常に動きデータが入出力されています。

まとめ

今回はJTAGの波形に関して紹介させていただきました。

記事をまとめますと下記になります。

ロジアナは1000円程度で購入可能です。

今回のJTAG含めて多くの通信インターフェースで測定・解析が可能です。

よろしければ皆さまも是非試してみてください

コメント