FPGAでOpenCVを試してみました。

使用したボードはXilinx(AMD)のKV260です。

Vitis Vision Libraryを使ってエッジ検出をした内容を紹介します。

FPGAでOpenCVを試したメモ。Xilinx(KV260)編

FPGAでOpenCVを試してみました。

テストしたのはエッジ検出(Canny Edge Detection)です。

Vitis Vision Libraryを使って写真からエッジ検出した内容を紹介します。

ハード環境

Xilinx(AMD)のKV260というFPGA評価ボードでテストしています。

- 評価ボード…KV260

このKV260は下記の第6回AIエッジコンテストで使用したFPGAボードです。

ソフト環境

ソフト環境は2023年版のプラットフォームで対応しています。

- Vivado 2023.1

- Vitis 2023.1

- Petalinux 2023.1

インストール方法に関しては下記で紹介した2022年版と同様にできました。

最新版にはアップデートしていませんが、(去年の)下記記事が参考になるかと思います。

KV260用のSDカードを作る

下記記事を参考にKV260のSDカードを作ります

筆者が今回のテストした時期の2023年の8月頭でした。

その時はXilinxの下記WikiページにKV260用にプレビルドしたイメージがありませんでした。

https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/1641152513/Kria+K26+SOM#PetaLinux

ビルド元のBSPファイルは下記にありますので、ダウンロードしてpetalinuxを動かします。

|

1 2 3 4 5 |

petalinux-create -t project -s xilinx-kv260-starterkit-v2023.1-05080224.bsp cd xilinx-kv260-starterkit-2023.1/ petalinux-build petalinux-package --boot --u-boot --force petalinux-package --wic --images-dir images/linux/ --bootfiles "ramdisk.cpio.gz.u-boot,boot.scr,Image,system.dtb,system-zynqmp-sck-kv-g-revB.dtb" --disk-name "mmcblk1" |

作成したSDイメージ(petalinux-sdimage.wic)をbalenaetcherなどを使って書き込みます。

/xilinx-kv260-starterkit-2023.1/images/linux の箇所にあります

OpenCVをKV260で試す

先駆者様の手法を真似て、まずは同様にKV260でOpenCVを動かしてみます。

実施した内容に関しては下記記事をご参考ください。

2022年度版でしたが、特に2023年の環境でも実施できました。

ダウンロードするファイルなどは異なるので、注意が必要です。

|

1 2 3 |

tar xzvf xilinx-zynqmp-common-v2023.1_05080224.tar.gz cd xilinx-zynqmp-common-v2023.1/ ./sdk.sh -d . |

確かKV260上で動かす際に一度エラーが出ました。

libxilinxopencl.so.2: cannot open shared object file: No such file or directory

|

1 2 |

xilinx-kv260-starterkit-20231:~$ ./resize test.jpg 480 640 ./resize: error while loading shared libraries: libxilinxopencl.so.2: cannot open shared object file: No such file or directory |

ネットで調べると公式に解決方法が記載されていました。

XRTをインストールし直すと動作しました。

参考記事同様に、opencvで写真をリサイズ(resize)するテストを実行できました。

opencvでリサイズした写真と元の写真のピクセル比率を確認テストしているようです。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 |

xilinx-kv260-starterkit-20231:~$ ./resize test.jpg 360 640 Input image height : 720 Input image width : 1280 INFO: Running OpenCL section. Found Platform Platform Name: Xilinx INFO: Device found - edge Input Image Bit Depth:8 Input Image Channels:1 NPPC:1 XCLBIN File Name: krnl_resize INFO: Importing ./krnl_resize.xclbin Loading: './krnl_resize.xclbin' 6.40347ms Minimum error in intensity = 0 Maximum error in intensity = 1 Percentage of pixels above error threshold = 0 Test Passed |

KV260+OpenCVでエッジ検出をしてみる

単純に真似ただけでは勿体ないので、違うパターンでもテストしてみます。

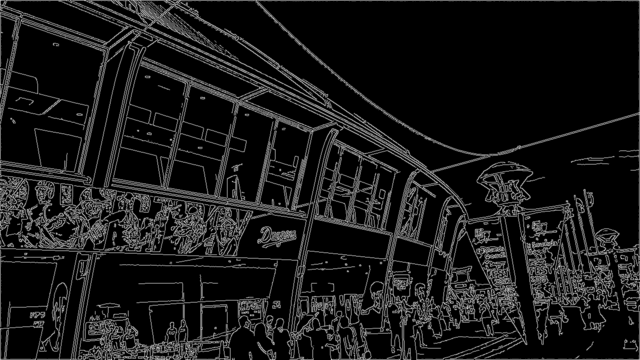

エッジ検出(Canny Edge Detection)をテストしています。

公式のソースコード・ベンチマーク結果などは下記リンク先です。

https://github.com/Xilinx/Vitis_Libraries/tree/master/vision/L2/examples/canny

https://xilinx.github.io/Vitis_Libraries/vision/2022.1/canny-bm.html

プラットフォームの作り方は参照したresizeの方法と同じです。

exampleの中に「Canny L2 Test」があります。

KV260に作成したプラットフォームのファイルと写真(test.jpg) を送ります。

|

1 2 3 4 5 6 7 8 9 |

iotengineer@iotengineer-Inspiron-3650:~/opencv/kv260_scp$ scp -r canny/ petalinux@192.168.11.5:~ petalinux@192.168.11.5's password: test.jpg 100% 256KB 34.1MB/s 00:00 512x512.jpg 100% 76KB 42.4MB/s 00:00 krnl_canny.xclbin 100% 7699KB 10.4MB/s 00:00 shell.json 100% 57 123.8KB/s 00:00 canny 100% 1215KB 66.2MB/s 00:00 krnl_canny.bin 100% 7699KB 50.5MB/s 00:00 pl.dtbo 100% 2552 5.0MB/s 00:00 |

あとはKV260上で実行するだけです。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 |

xilinx-kv260-starterkit-20231:~$ cd canny/ xilinx-kv260-starterkit-20231:~/canny$ sudo mkdir /lib/firmware/xilinx/canny Password: xilinx-kv260-starterkit-20231:~/canny$ sudo cp shell.json krnl_canny.bin pl.dtbo /lib/firmware/xilinx/canny/ xilinx-kv260-starterkit-20231:~/canny$ sudo xmutil listapps Accelerator Accel_type Base Base_type #slots(PL+AIE) Active_slot resize XRT_FLAT resize XRT_FLAT (0+0) -1 k26-starter-kits XRT_FLAT k26-starter-kits XRT_FLAT (0+0) 0, canny XRT_FLAT canny XRT_FLAT (0+0) -1 xilinx-kv260-starterkit-20231:~/canny$ sudo xmutil unloadapp remove from slot 0 returns: 0 (Ok) xilinx-kv260-starterkit-20231:~/canny$ sudo xmutil loadapp canny canny: loaded to slot 0 xilinx-kv260-starterkit-20231:~/canny$ ./canny test.jpg Input image height : 720 Input image width : 1280 Found Platform Platform Name: Xilinx Input Image Bit Depth:8 Input Image Channels:1 NPPC:1 XCLBIN File Name: krnl_canny INFO: Importing ./krnl_canny.xclbin Loading: './krnl_canny.xclbin' 14.3718ms Latency for CPU function is: 77.970ms Minimum error in intensity = 0.000 Maximum error in intensity = 255.000 Percentage of pixels above error threshold = 0.051 No of Pixels with Error = 469 kernel done Test Passed .... !!! |

もともとの写真が下記です。下記記事で使っていたナゴヤドームの写真です。

ナゴヤドームの内野SSの見え方。一塁側の座席で見やすかった件

OpenCVでエッジ検出したのが下記です。無事できました。

まとめ

FPGA(KV260)を使ってOpenCVでエッジ検出してみました。

Vitis Vision Libraryには色々なサンプル例があります。

もし興味ある方はぜひ同様にテストしてみてください。

コメント