FPGAボードのKV260でGPIOを制御してみました。

Python(PYNQ)経由でPMODコネクタからLED出力・SW入力しています。

簡単にテストした内容を紹介します。

KV260とPYNQでGPIOを制御してみたメモ

AMD(Xilinx)のFPGAボードであるKV260には、PMODコネクタがあります。

市販のジャンパーワイヤーを使えば、GPIOとしても使用することができます。

オスのジャンパーを挿すだけです。簡単に接続できます。

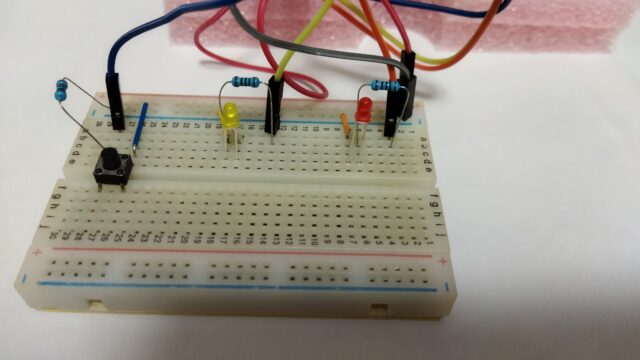

あとはブレッドボード+LED・SWにでも接続すれば、出力・入力テストが簡単に可能です。

Python(PYNQ)経由でGPIO制御することができます。

プロジェクトの作成から、実際のテストまで紹介します。

実際にKV260でGPIOを動かす様子を動画にしてアップしています。

VivadoでKV260のプロジェクトを作る

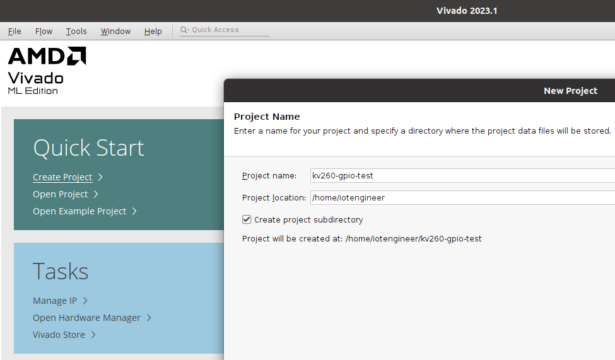

Vivadoを開いて、プロジェクトを作成していきます。

Create Project

「Create Project」→適当な名前つけて進めていきます。

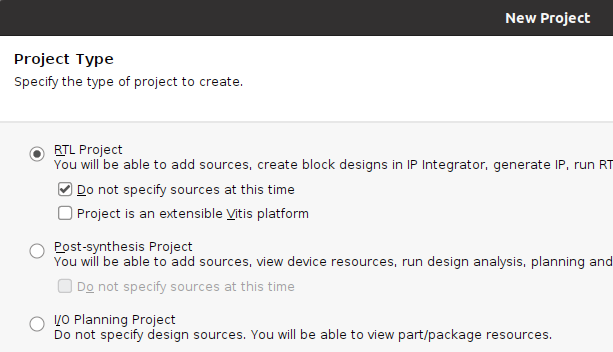

Project Typeでは、(とりあえず)デフォルトのRTLにしておく。

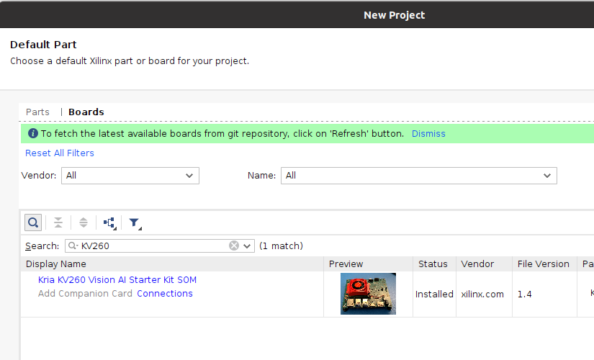

Default Partでは、Boardを選択してKV260を選ぶ。

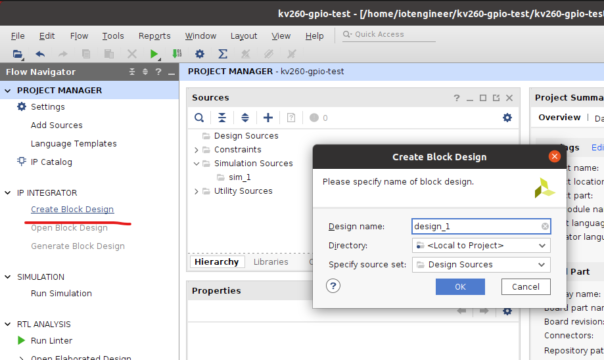

Create Block Design

Projectファイルが出来上がります。

Create Block Designを選択して、ブロックのデザインを進めます。

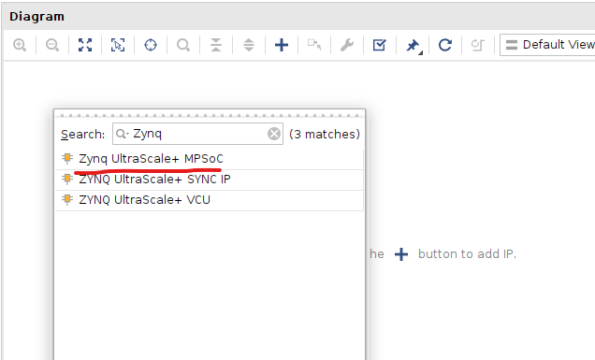

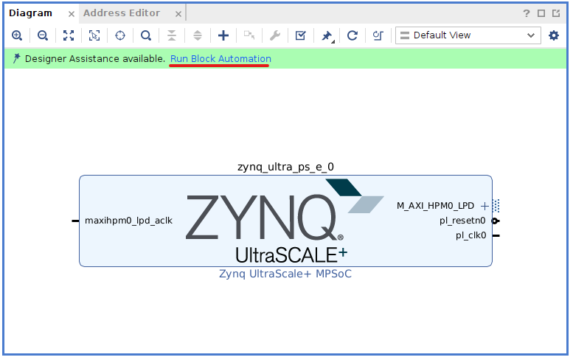

Zynq UltraScale+ MPSoCを選んで、「Run Block Automation」を選択する。

Optionsの箇所にApply Board Presetにチェックが入っている。

デフォルトでOKを選択。

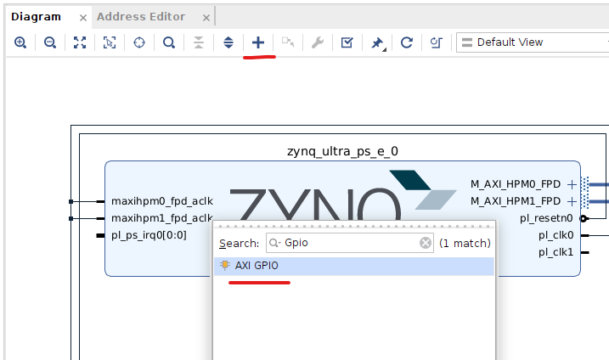

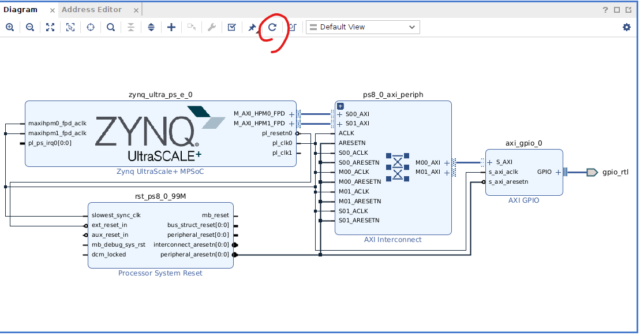

新たに「+」からAXI GPIOのIPを選択

Run connection AutomationからデフォルトでOKを選びます。

リセットやAXIなどのIPが勝手に配置されます。

更新ボタンのような「Regenerate Layout」をクリックすると綺麗に配置されます。

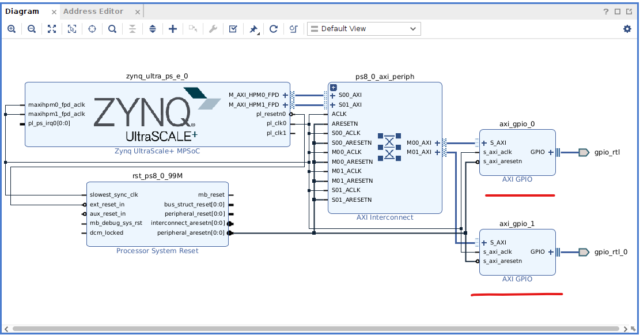

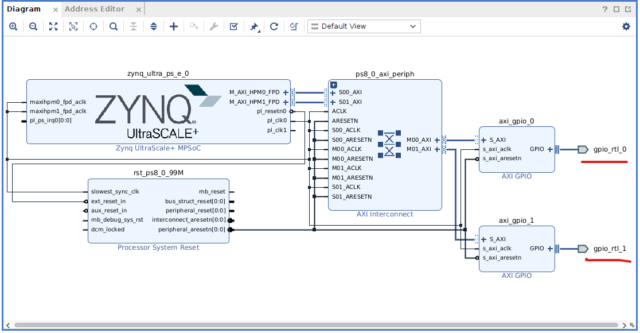

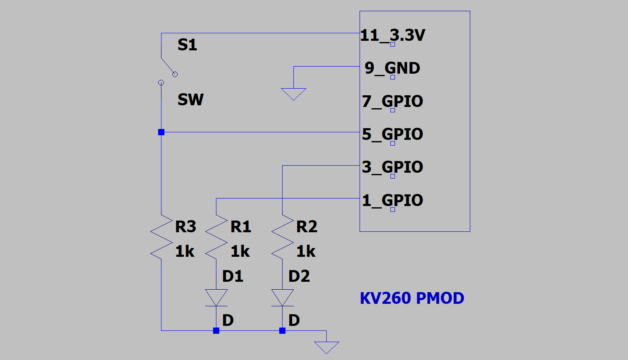

今回は2個のGPIO_IPをPMODコネクタから出力させます。

AXI GPIOを追加でコピーして、もう一度Run connection Automationを行います。

GPIOの名前も、IPの番号に合わせておきました。

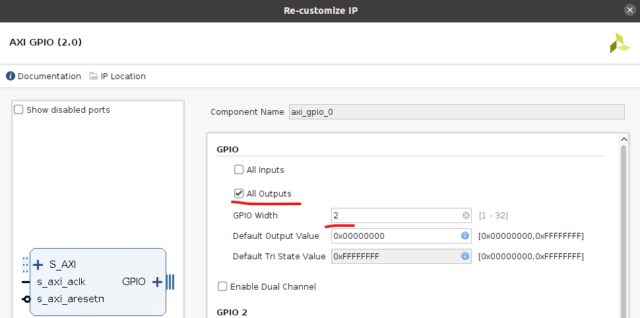

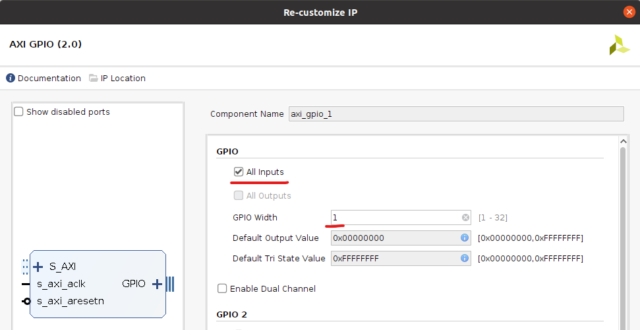

デフォルトだとGPIOが32本のバスになっています。

今回は各IPでOUTPUT2本とINPUT1本で使いますので、GPIO Widthを設定しました。

またAll outputs ,All inputs にもチェックを入れています。

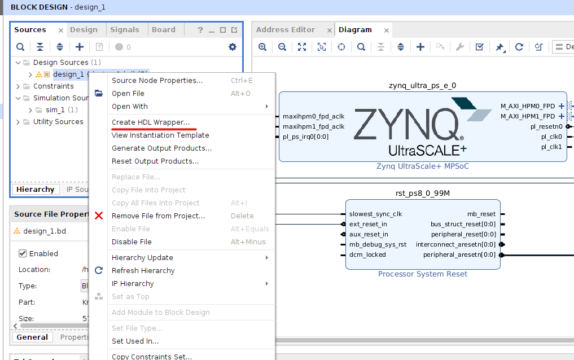

Create HDL Wrapper

Sourceのデザインを右クリックして、Create HDL Wrapperします。

何かoptionsのウインドウが出るかもしれませんが、デフォルトで進めます。

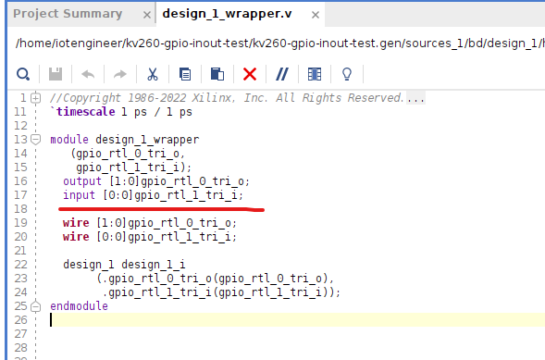

IPブロックのデザインから、入出力につながるHDLが作られます。

作られたファイルを確認すると,各GPIOからのoutput,inputが確認できます。

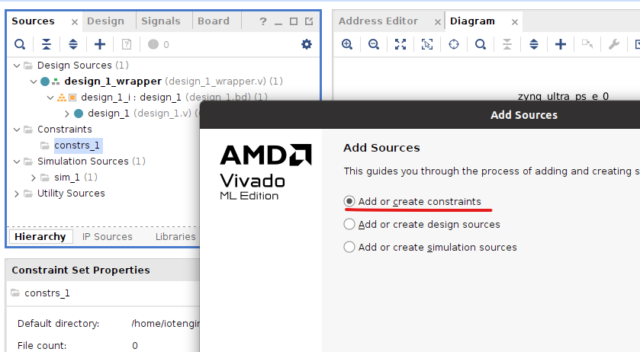

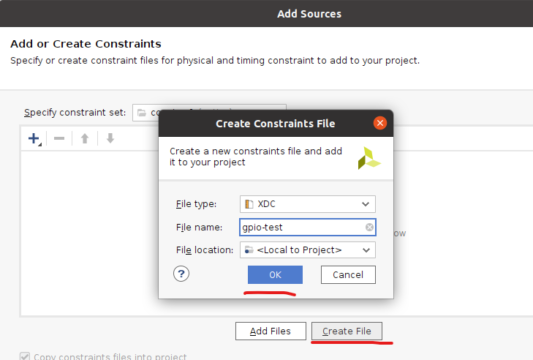

XDCファイルを作成する

ピンアサインをしていきます。

Constrainsの箇所で右クリックしてAdd Sorucesから設定します

Create FileでXDCファイルを追加します。

今回はPMODの1ピン(H12)と3ピン(E10)と5ピン(D10)を設定しています。

- 入力…5ピン(D10)

- 出力…1ピン(H12),3ピン(E10)

|

1 2 3 4 5 6 7 |

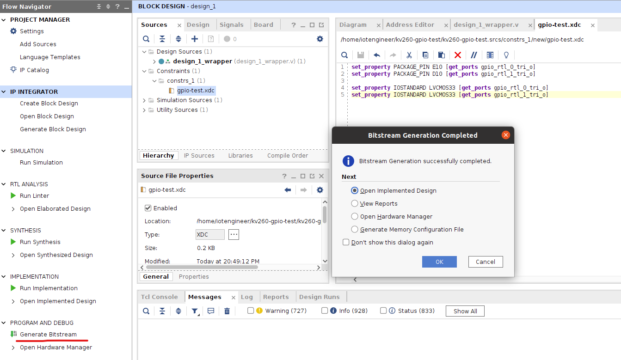

set_property PACKAGE_PIN E10 [get_ports gpio_rtl_0_tri_o[0]] set_property PACKAGE_PIN H12 [get_ports gpio_rtl_0_tri_o[1]] set_property PACKAGE_PIN D10 [get_ports gpio_rtl_1_tri_i[0]] set_property IOSTANDARD LVCMOS33 [get_ports gpio_rtl_0_tri_o[0]] set_property IOSTANDARD LVCMOS33 [get_ports gpio_rtl_0_tri_o[1]] set_property IOSTANDARD LVCMOS33 [get_ports gpio_rtl_1_tri_i[0]] |

PMODのピンを確認

下記、先駆者様の記事同様に使うPMODのピンを確認しました。

この場を借りてお礼申し上げます。

https://zenn.dev/ryuz88/articles/kv260_led_blinking

AMDの公式ページから回路図とXDCファイルを見比べて確認していきます。

https://japan.xilinx.com/products/som/kria/k26c-commercial.html#documentation

XTP682 - Kria KV260 Starter Kit Carrier Card Schematics (v1.2)

XTP685 - Kria K26 SOM XDC File (v1.0)

回路図とXDCファイルを見比べて、使うピンを探しました。

PMODの1ピン(H12)、3ピン(E10)、5ピン(D10)がIOBank45(3.3V)のため使えました。

Bitstreamを作成

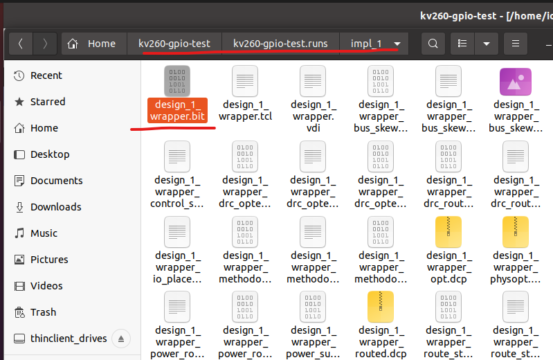

Generate Bitstreamのファイルを作成します。エラーなければ作成できます。

おそらくプロジェクトの~.runs/impl_1/あたりにbitファイルができます。

今回筆者の場合は「~/kv260-gpio-test/kv260-gpio-test.runs/impl_1」でした。

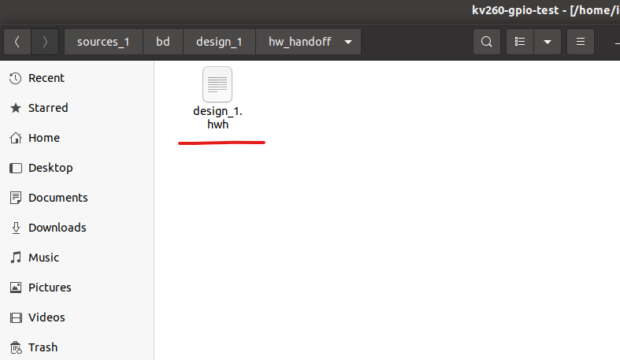

hwhファイルを作成

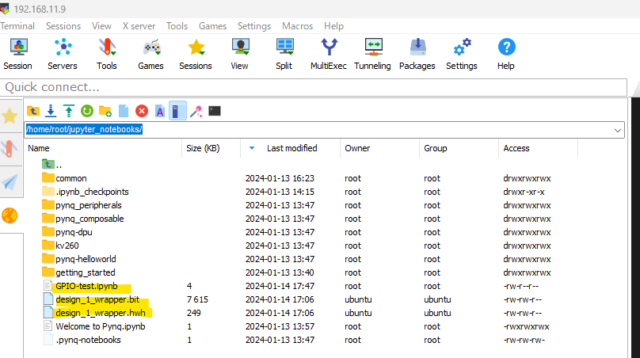

ハードウェアの情報が入っている.hwhファイルも必要になります。

Bitstreamを作った後に下記例のプロジェクトフォルダにあるはずです。

~/kv260-gpio-test/kv260-gpio-test.gen/sources_1/bd/design_1/hw_handoff

RuntimeError: Unable to find metadata for bitstream

.hwfファイルは必ず、名前をBitstream.bitを合わせて名前変更しておきます。

筆者の場合は、下記のように合わせておきました。

- design_1_wrapper.bit

- design_1.hwh→design_1_wrapper.hwh

公式のドキュメントにも記載されています。

https://pynq.readthedocs.io/en/latest/overlay_design_methodology/overlay_design.html#overlay-design

もし合わせておかないと、PYNQ実行時に下記のようなエラーが発生しました。

RuntimeError: Unable to find metadata for bitstream

|

1 2 3 4 5 6 |

--------------------------------------------------------------------------- RuntimeError Traceback (most recent call last) Input In [3], in <cell line: 3>() 1 from pynq import Overlay 2 from pynq.lib import AxiGPIO ----> 3 ol = Overlay("/home/root/jupyter_notebooks/design_1_wrapper.bit") |

|

1 2 3 4 5 6 7 |

File /usr/local/share/pynq-venv/lib/python3.10/site-packages/pynq/pl_server/embedded_device.py:692, in EmbeddedDevice.get_bitfile_metadata(self, bitfile_name, partial) 690 parser = _get_bitstream_handler(bitfile_name).get_parser(partial=partial) 691 if parser is None: --> 692 raise RuntimeError("Unable to find metadata for bitstream") 693 return parser RuntimeError: Unable to find metadata for bitstream |

PMODコネクタからGPIO

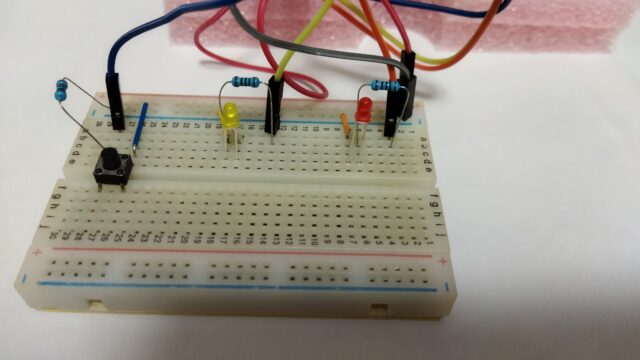

今回の接続ではブレッドボード、ジャンパーワイヤー、SW、LED・抵抗を用意しました。

抵抗に関しては全て1kΩ品です。

簡単に回路図を書き直すと下記形です。非常にシンプルな形です。

下記のような汎用の電子工作キットに入っているもので足りるはずです

KV260のプラットフォーム(SDカード)

KV260へのSDカードを用意します。

Ubuntu Desktop 22.04 LTS

今回は下記で提供されているのKV260デフォルトのUbuntuを使っています。

Kria™K26 SOMs(KR260/KV260) → Ubuntu Desktop 22.04 LTS

Kria-PYNQ

SDカードを入れてKV260を立ち上げたら、Kria-PYNQをインストールします。

約30分ぐらいで結構時間がかかります。GitHubのリンク先は下記です。

https://github.com/Xilinx/Kria-PYNQ

公式通りの下記手順でインストールしました。

|

1 2 3 |

git clone https://github.com/Xilinx/Kria-PYNQ.git cd Kria-PYNQ/ sudo bash install.sh -b KV260 |

テスト動画

今回のKV260でGPIOを動かす様子を動画にしてYoutubeにもアップしています。

よろしければ、一緒に下記もご覧ください。

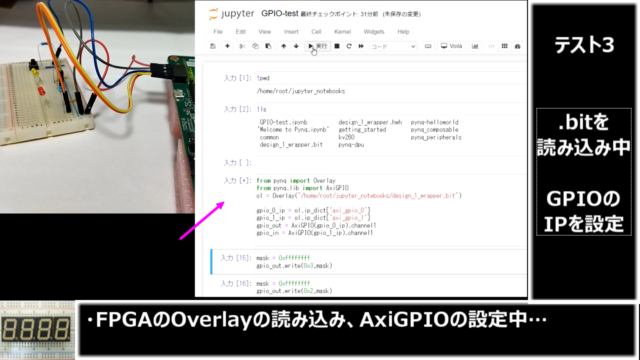

Jupyter Notebook

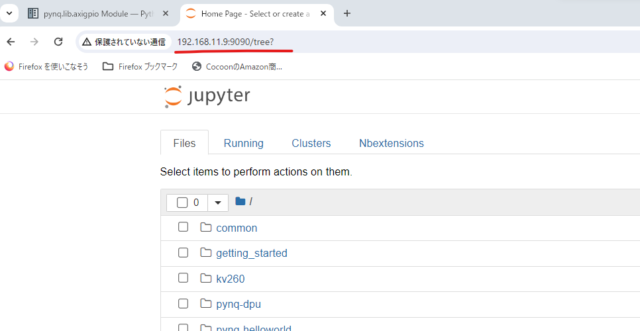

Kria-PYNQをJupyter Notebookから使って、GPIOを制御します。

KV260にはLANケーブルがあるので、LANで繋げてブラウザ経由で編集していきます。

LANケーブルからWebブラウザ経由で操作した方が楽です

インストール後にifconfigなどでIPアドレスを確認します。

今回筆者の場合IPアドレスは「192.168.11.9」でした。

Webブラウザ(筆者の場合はChrome)で「http://192.168.11.9:9090/」と入力します。

Jupyter Notebookが表示されます。デフォルトだとフォルダは下記にあるはずです。

/home/root/jupyter_notebooks/

※筆者はこのフォルダにVivadoで作成した.bitと.hwlファイルを置きました。

新規のNotebookを作成したい場合は、右上にある「New」箇所をクリックします。

「Python 3(ipykernel)」を選びます。

ipynbファイル

今回筆者が作成・実行したipynbファイルは下記です。Gistにアップしています。

AxiGPIO

Vivadoで作成した(.bit)ファイルを読み込んだ後にAXI-GPIOのIPを制御しています。

PYNQのライブラリにAXI-GPIOがあります。

AXI-GPIOの操作方法の公式は下記です。

https://pynq.readthedocs.io/en/latest/pynq_package/pynq.lib/pynq.lib.axigpio.html#pynq-lib-axigpio

ipynbの3つ目の手順です。

AxiGPIOをインポート→GPIOのIPを指定→channel1を指定しています。

|

1 2 3 4 5 6 7 8 |

from pynq import Overlay from pynq.lib import AxiGPIO ol = Overlay("/home/root/jupyter_notebooks/design_1_wrapper.bit") gpio_0_ip = ol.ip_dict['axi_gpio_0'] gpio_1_ip = ol.ip_dict['axi_gpio_1'] gpio_out = AxiGPIO(gpio_0_ip).channel1 gpio_in = AxiGPIO(gpio_1_ip).channel1 |

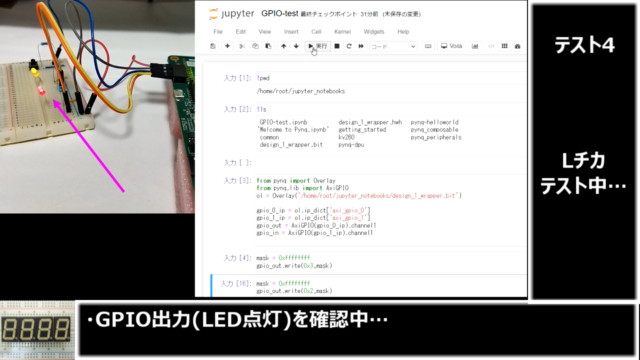

LED出力の箇所はWriteしています。ipynbの4~7つ目の手順です。

今回2出力(2bit)のため、0x3→0x2→0x1→0x0 とLEDを点灯・消灯させました。

|

1 2 |

mask = 0xffffffff gpio_out.write(0x3,mask) |

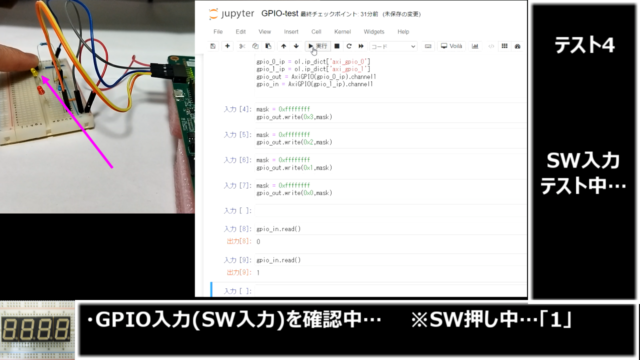

SW入力の箇所はReadしています。

SW押している時は「1」が、押していないときは「0」が確認できます。

|

1 |

gpio_in.read() |

まとめ

FPGAボードのKV260でGPIOを制御してみました。

Python(PYNQ)経由でPMODコネクタからLED出力・SW入力しています。

よろしければ皆様もテストしてみてください。

またジャンパー配線ではなく、簡単な基板作ってPMODコネクタに接続してみました。

下記記事で紹介しています。

PCBGOGOへのガーバーデータをKiCadから作成したメモ

コメント