デバッグ用のインターフェースとして使われるJTAGとSWDの差異を確認してみました。

両方の信号をロジアナで解析をしています。

通信速度からプロトコルの中身まで、実際の波形交えて紹介していきます。

JTAGとSWDの違いは?各ケーブルの信号を解析してみた

JTAGとSWDの大きな違いとしては信号線の本数が異なります。

JTAGが4本で、SWDが2本です。

JTAGの「TDI,TDO,TMS」の3本が、SWDの「SWDIO」の1本に集約されたイメージです。

- JTAG「TCK」⇔SWD「SWCLK」

- JTAG「TDI,TDO,TMS」⇔SWD「SWDIO」

JTAGは基本的にTDI,TDO,TCK,TMSの4本の信号で通信します。

※JTAG…Joint Test Action Group

CPUやFPGAのデバッグ用のインターフェースとしてよく使われています。

SWDの信号線はSWDIO(データ)とSWCLK(クロック)の2本です。

※SWD…Serial Wire Debug

ARMのデバッグ用のインターフェースとして使われているケースが多いです。

JTAGとSWDの違いを解析した結果含めて、詳しく紹介していきます。

JTAGの信号解析

JTAGの信号であるTDI,TDO,TCK,TMSの波形をロジアナで測定してみました。

- TDI…Test Data In

- TDO…Test Data Out

- TCK…Test Clock

- TMS…Test Mode Select

実際にJTAG通信をロジアナで測定した動画も下記で紹介しています。

信号解析できている様子が分かりますので、是非合わせてご覧ください。

JTAGのケーブル

今回JTAGのテストで使用したケーブルはJTAG-HS2です。

XilinxのFPGAにプログラムを書き込むためのツールです。

パソコンからUSB→JTAG変換してFPGAと通信することが可能です。

Xilinxの評価ボードメーカとしても有名なDiligent製のケーブルとなります。

下記記事で詳細を紹介しています。

XilinxをJTAG-USBケーブルで書き込み!JTAG-HS2を試してみた

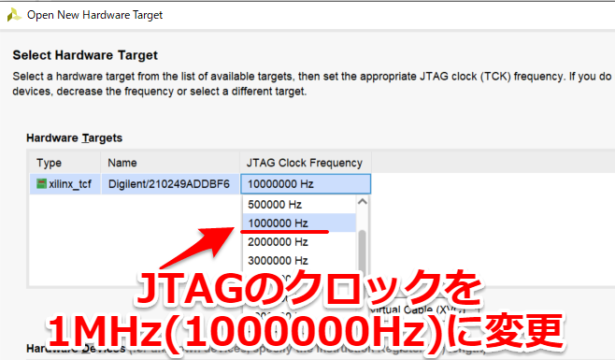

JTAGの通信速度

JTAGの通信速度(クロック)であるTCKが設定した値になっていることを確認します。

今回のロジアナは安い趣味用ですので、デフォルトの10MHzから1MHzに変更しています。

TCKの周波数1MHz(周期1us)であることを測定出来ました。

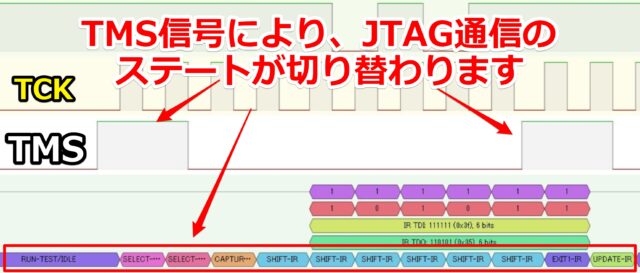

JTAGのステートを確認する

TMSはJTAGデバイスのコントローラ(TAPコントローラ)の状態遷移に使われます。

※TMS…Test Mode Select

TMS信号により、JTAG通信のステートが切り替わります。

全てのJTAG(TAPコントローラ)のステートは難しいですが、部分的にでも確認していきます。

TMS信号はステートの状態遷移に使われます。

最初にTMS信号が入ってリセットがかかる箇所を中心に確認していきます。

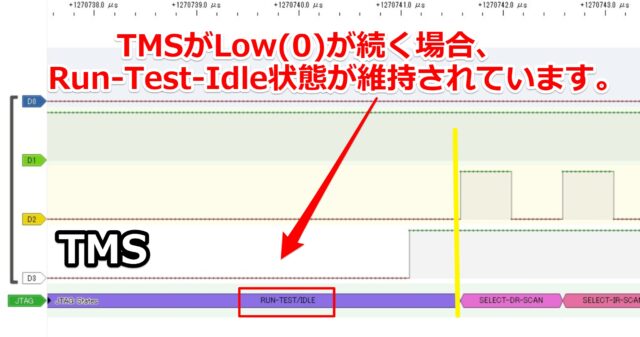

Run-Test-Idle

TMSがLow(0)が続く場合、「Run-Test-Idle」のアイドル状態が維持されています。

TMSをHi(1)にすることでステートが遷移することを確認出来ました。

Test-Logic-Reset

TMSをHi(1)後に「Select-DR-Scan」「Select-IR-Scan」に移行しています。

その後「Test-Logic-Reset」のステートに遷移してリセットをしています。

(仕様通りに)TCKの5回分、TMSがHi(1)を維持していることを確認できました。

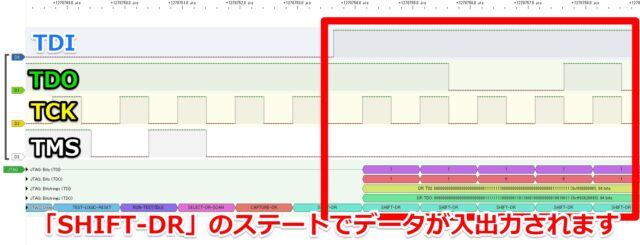

SHIFR-DR

リセットが終わった後は、再度TMSが動きます。

「Run-Test-Idle」「Select-DR-Scan」「Capture-DR」の順でステートが遷移しています。

そして「SHIFT-DR」でTMSはLow(0)を維持して、データが入出力されています。

他にも多くのステート・状態遷移があります。(全16ステート)

今回紹介したのはあくまで、ほんの一部であることをご了承下さい。

JTAGとロジアナの接続・設定方法などについては下記記事で説明しています。

SWDの信号解析

SWDの信号であるSWDIOとSWCLKの波形もロジアナで測定してみました。

SWDIO…Serial Wire Debug Input Output

SWCLK…Serial Wire Clock

実際にSWD通信をロジアナで測定した動画も下記で紹介しています。

信号解析できている様子が分かりますので、是非合わせてご覧ください。

SWDのケーブル

SWDのケーブルに関してはラズパイを利用しました。

「ラズパイ」からジャンパー線を飛ばして「ラズパイPico」に接続しています。

ラズパイPicoはSWDの通信インターフェースを持っています。

ラズパイPicoの使い方に関しては下記記事でも紹介しています。

SWDのデバッガはOPENOCD

今回のテストではOPENOCDというオープンソースのデバッガで対応しています。

ラズパイPicoに初期通信するタイミングでロジアナを測定しています。

ラズパイPicoへのSWD通信に関しては下記ラズパイ公式のドキュメントを参考にしています。

https://datasheets.raspberrypi.org/pico/getting-started-with-pico.pdf

Chapter 5. Debugging with SWD

SWDの接続方法

ラズパイとPicoのSWD接続は下記形になっています。

ロジアナ含めてジャンパー線とICクリップ-ワニ口で接続しています。

- ラズパイ_22ピン→Pico_SWCLK

- ラズパイ_20ピン→Pico_GND

- ラズパイ_18ピン→Pico_SWDIO

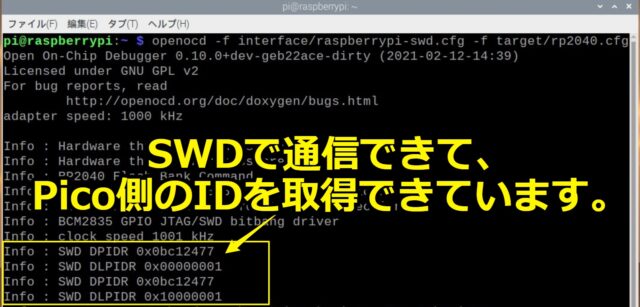

ラズパイのOPENOCDの結果

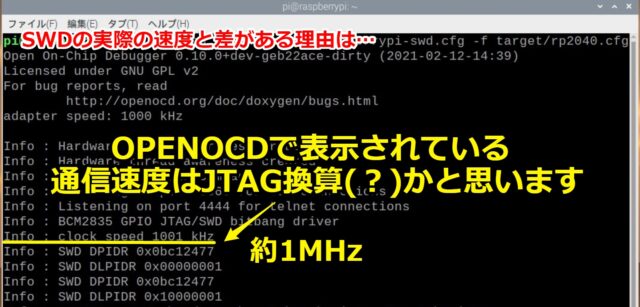

ラズパイからPicoにOPENOCDの通信コマンドを打った時の時の結果です。

SWDで正常に通信できていると、Pico側からIDを取得できています。

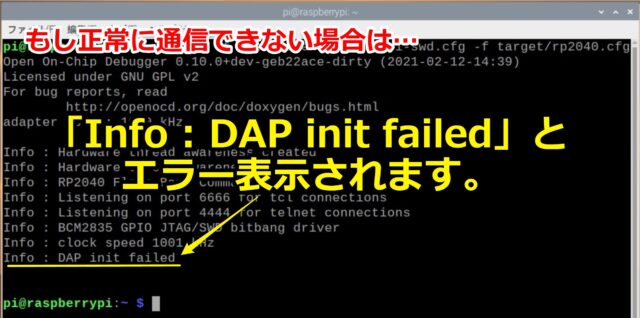

もし正常に通信できない場合は「Info : DAP init failed」とエラー表示されます。

SWDが接続できたログ

SWDが接続できたコマンドのログを貼り付けておきます。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 |

pi@raspberrypi:~ $ openocd -f interface/raspberrypi-swd.cfg -f target/rp2040.cfg Open On-Chip Debugger 0.10.0+dev-geb22ace-dirty (2021-02-12-14:39) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.html adapter speed: 1000 kHz Info : Hardware thread awareness created Info : Hardware thread awareness created Info : RP2040 Flash Bank Command Info : Listening on port 6666 for tcl connections Info : Listening on port 4444 for telnet connections Info : BCM2835 GPIO JTAG/SWD bitbang driver Info : clock speed 1001 kHz Info : SWD DPIDR 0x0bc12477 Info : SWD DLPIDR 0x00000001 Info : SWD DPIDR 0x0bc12477 Info : SWD DLPIDR 0x10000001 Info : rp2040.core0: hardware has 4 breakpoints, 2 watchpoints Info : rp2040.core1: hardware has 4 breakpoints, 2 watchpoints Info : starting gdb server for rp2040.core0 on 3333 Info : Listening on port 3333 for gdb connections |

SWDが接続できなかったログ

わざとSWDが接続しなかった際のコマンドのログを貼り付けておきます。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

pi@raspberrypi:~ $ openocd -f interface/raspberrypi-swd.cfg -f target/rp2040.cfg Open On-Chip Debugger 0.10.0+dev-geb22ace-dirty (2021-02-12-14:39) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.html adapter speed: 1000 kHz Info : Hardware thread awareness created Info : Hardware thread awareness created Info : RP2040 Flash Bank Command Info : Listening on port 6666 for tcl connections Info : Listening on port 4444 for telnet connections Info : BCM2835 GPIO JTAG/SWD bitbang driver Info : clock speed 1001 kHz Info : DAP init failed |

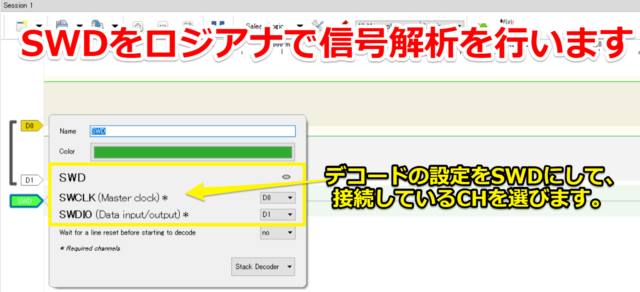

SWDをロジアナで信号解析を行う

SWDの信号解析をするためにロジアナの設定を行います。

デコードの設定をSWDにして、SWCLKとSWDIOに接続しているCHを選びます。

今回の個人で使えるロジアナ・ソフトに関しては下記記事で紹介しています。

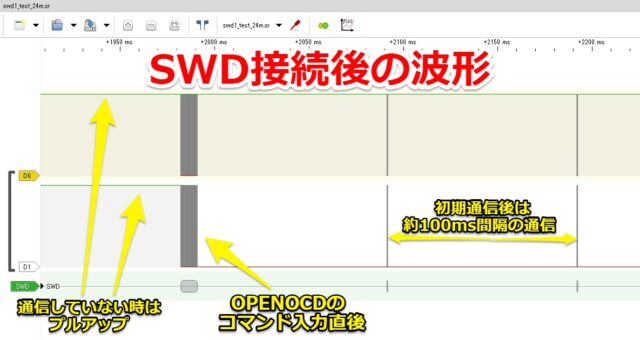

先述したOPENOCDのコマンド前後では下記波形になります。

何も通信していない状態はプルアップされて、コマンド入力時には一定の通信が見られます。

その後、待機(アイドル)状態では約100ms間隔で通信していました。

今回はOPENOCDのコマンド直後の波形を解析していきます。

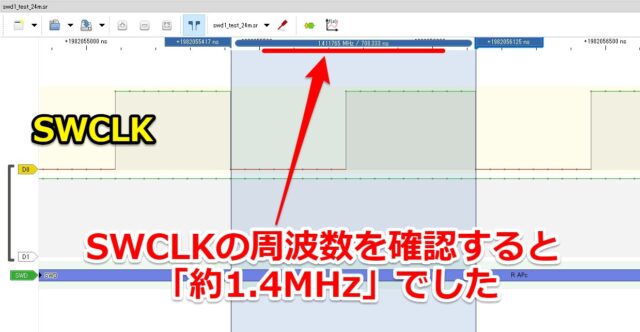

SWDの通信速度

波形をアップしてSWCLKの周波数を確認すると「約1.4MHz」でした。

ただ、OPENOCDのコマンドの結果では1.001kHz「約1MHz」という表示でした。

おそらくこの差分に関しては、表示されている通信速度がJTAG換算のためかとは思います。

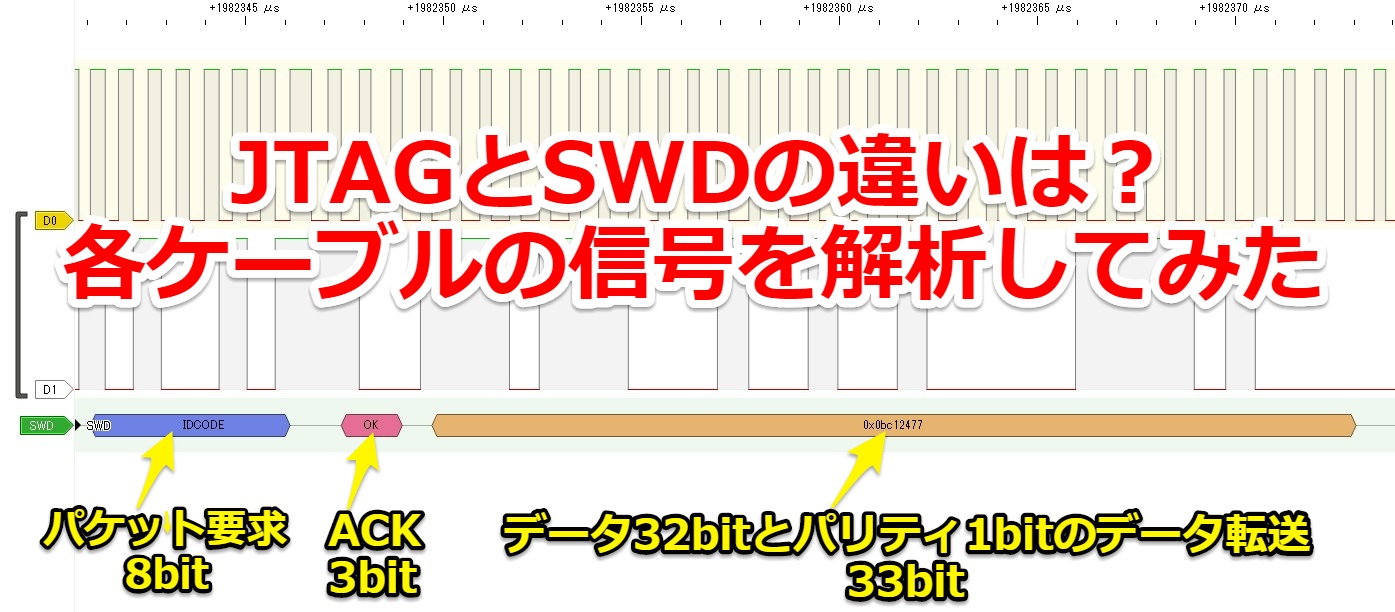

SWDのプロトコル

SWDではデータ線がSWDIOの1本しかありません。

ReadかWriteかを判断するためには、データの頭にパケットが必要になります。

ARMのSWDのプロトコルを規格書から見ると下記形になります。

- ホストからターゲットへの 「8 bit」のパケット要求

- ターゲットからホストへの 「3 bit」のACK応答

- データ32bitとパリティ1bitの「33 bit」データ転送

- パケット・ACK・データの隙間のTrn(Turnaround)も考慮すると「2bit」

素のデータ量「32bit」と比べると、SWDのデータ量は(8+3+33+2)/32≒約1.4倍になる。

そのため、SWDの実通信速度が1MHz→約1.4MHzとなっていそうです。

(もし計算・考えが間違っていたら、ページ末尾箇所にコメントしてもらえると幸いです)

SWDの仕様・規格について

ARMの公式HPにSWD含めたデバッグのインターフェースのドキュメントがあります。

もしARMのSWDの仕様を詳しく調査したい方は下記からダウンロードすると良いと思います。

https://developer.arm.com/documentation/

ARM Debug Interface Architecture Specification ADIv*.*

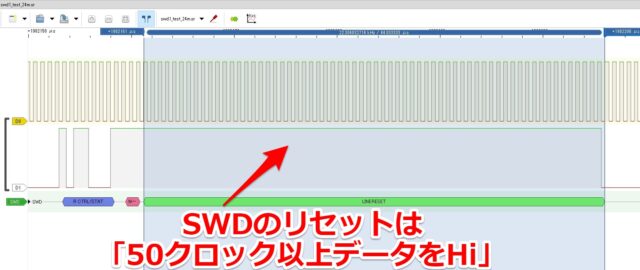

SWDのリセット

SWDのリセット(LINERESET)に関しては「50クロック以上データをHi」にします。

実際のSWDのリセットを確認すると、約64クロック程度Hiになっていました。

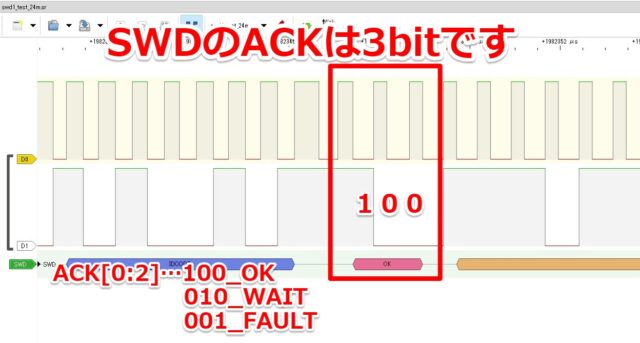

SWDのACK

SWDのACKは3bitで構成されています。

ACK[0:2]が「100_OK」「010_WAIT」「001_FAULT」となります。

下記例ではACKは「100_OK」となっていました。

まとめ

今回はJTAGのSWDの違いに関して紹介させていただきました。

記事をまとめますと下記になります。

ロジアナは1000円程度で購入可能です。

今回のJTAG・SWD含めて多くの通信インターフェースで測定・解析が可能です。

よろしければ皆さまも是非試してみてください

コメント