ラズパイ5のUARTのコネクタケーブルを作ってみました。

本来はラズパイの専用デバッグケーブルに付属してくるものです。

JSTのSHの3ピンですが、コネクタを自作して対応してみました。

ラズパイ5 UARTのコネクタケーブルを自作してみた。JSTのSHの3ピン編

ラズパイ5のUARTのコネクタを作ってみました。

本来はラズパイの専用デバッグケーブルに付属してくるものです。

JSTのSHの3ピンですが、コネクタを自作して対応してみました。

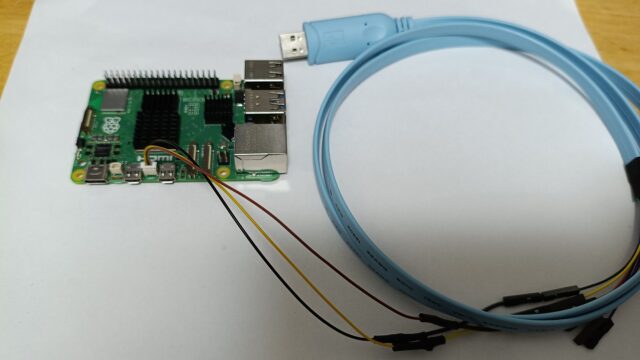

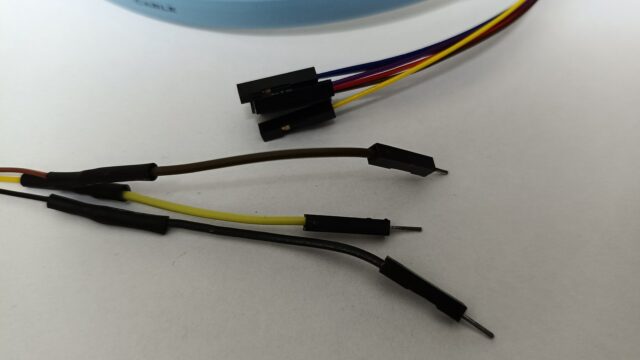

中継ケーブルの詳細を紹介します。

ラズパイの公式デバッガ

公式のラズパイのデバッガは何処でも購入可能です。

その中にJSTの3ピンでも接続できるケーブルも付属されています。

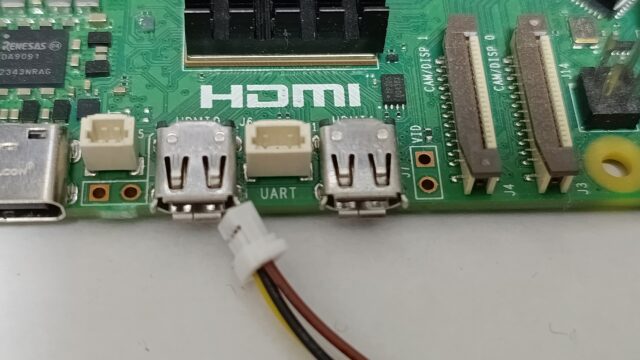

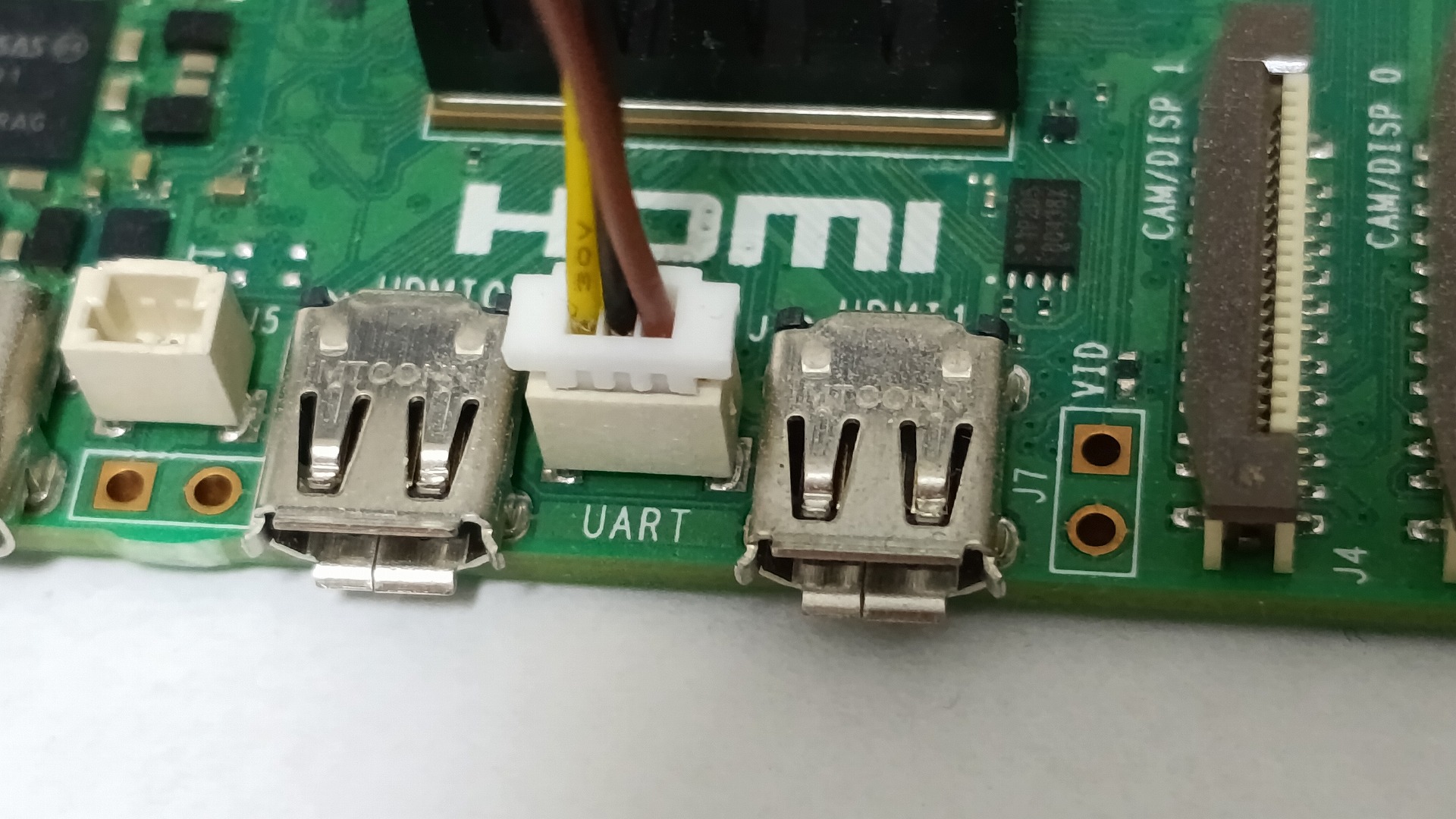

JSTのSHの3ピンコネクタ

但し、接続コネクタとしては汎用のコネクタです。

1.0mmピッチのJST「SH」3ピンコネクタの「BM03B-SRSS-TB」です。

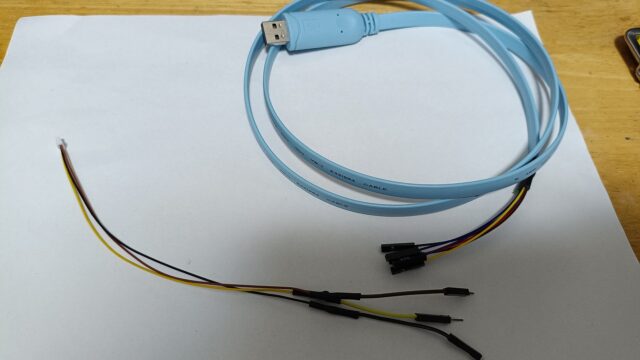

UARTシリアルケーブルを既に所持していれば、変換ケーブルでも対応可能です。

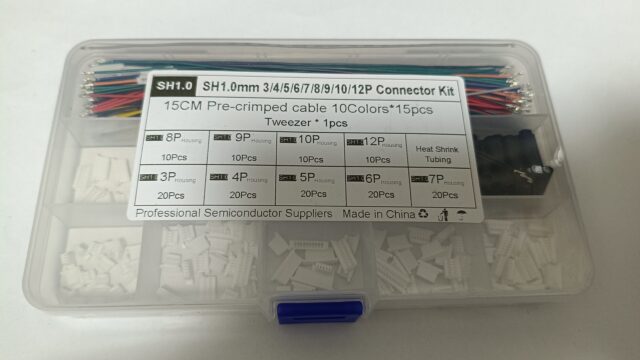

今回筆者は、SHのコネクタキットを持っていたのでそちらで対応しました。

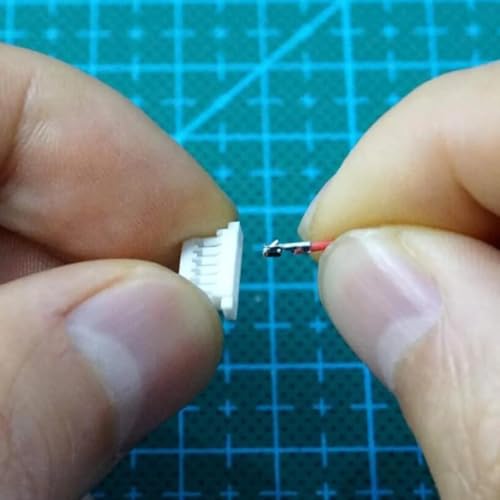

1㎜ピッチで細いケーブルなので、本来は作成+カシメるのもコツがいります。

そのため趣味では、差し込むだけのキットを使っています。

各SHコネクタが揃っていますので、色々電子工作したい方にはおススメです。

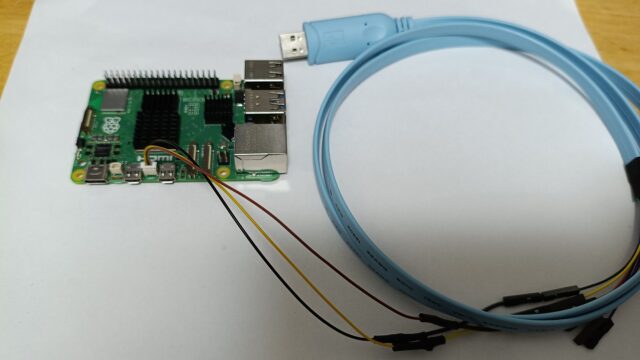

UART中継ケーブルを自作してみる

ラズパイのデータシートを見てピン配置を確認していきます。

デバッグコネクタの公式仕様

ラズパイ公式のデバッグコネクタについては、下記に記載されています。

詳細は下記をご確認ください。

https://datasheets.raspberrypi.com/debug/debug-connector-specification.pdf

NotebookLMでのまとめ

NotebookLMで簡単にまとめてもらった内容が下記です。

Raspberry Piの3ピンデバッグコネクタ仕様に基づき、中継ケーブル(コネクタ間ケーブル)を作成する際の注意点をまとめました。

- 適切なコネクタの選定: 1.0mmピッチのJST「SH」3ピンコネクタ(またはその互換品)を使用する必要があります。仕様書では、トップエントリー型(BM03B-SRSS-TB)やサイドエントリー型(SM03B-SRSS-TB)が例示されています。

- ケーブルの長さに注意: 信号の整合性を保つため、ケーブル長は数十センチメートル程度に抑えることが推奨されます。この範囲内であれば、約30MHzの動作パフォーマンスを維持することが可能です。

- ピンアサインの遵守: ターゲット側の視点で、各ピンは以下の役割を持っています。

- ピン1: UART RX / ケーブル側はTX

- ピン2: GND

- ピン3: UART TX / ケーブル側はRX

- 終端抵抗の扱い: 仕様では各デバイスのICピン付近に100Ωのソース終端抵抗を配置することになっています。ケーブル内に抵抗を入れる必要はありませんが、基板上の抵抗から抵抗までの総配線(PCBトレース+ケーブル)を最短にすることで、信号の品質が向上します。

UARTケーブルに接続できるように改造

今回は趣味のため、IC近くの100Ω終端抵抗は省略しています。

本当に中継ケーブルを作成・改造したのみです。

JSTの3ピンにケーブルを差し込んでいきます。

またUARTケーブルにピン接続できるように少しはんだ付けしました。

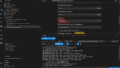

実際にUARTデバッグしてみる

中継ケーブル作成したら、実際にUARTデバッグしてみます。

ラズパイ5からは汎用GPIOの40ピンはSOC直接ではなくPCIE経由になりました。

但し、このUARTはSOC直接接続なので、そのままデバッグできます

実際にUARTシリアル接続できました。

下記別記事の内容ですが、問題なくブート時からのシリアルメッセージを取得できました。

RTOSとしての応答速度を比較してみた(Zephyrでのベンチマーク)

https://misoji-engineer.com/archives/rtos-speed-benchmark.html

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144 145 146 147 148 |

0.44 RPi: BOOTSYS release VERSION:4b019946 DATE: 2024/11/12 TIME: 16:10:44 0.48 BOOTMODE: 0x06 partition 0 build-ts BUILD_TIMESTAMP=1731427844 serial d04bb938 boardrev c04170 stc 848242 0.58 AON_RESET: 00000003 PM_RSTS 00001000 0.65 RP1_BOOT chip ID: 0x20001927 0.68 PM_RSTS: 0x00001000 0.68 part 00000000 reset_info 00000000 0.72 PMIC reset-event 00000000 rtc 00000000 alarm 00000000 enabled 0 0.78 uSD voltage 3.3V 0.97 Initialising SDRAM rank 2 total-size: 32 Gbit 4267 (0x15 0x00) 1.01 DDR 4267 1 0 32 152 BL:-1 2.42 OTP boardrev c04170 bootrom a a 2.43 Customer key hash 0000000000000000000000000000000000000000000000000000000000000000 2.50 VC-JTAG unlocked 2.73 RP1_BOOT chip ID: 0x20001927 3.01 RP1_BOOT chip ID: 0x20001927 3.01 RP1_BOOT: fw size 45984 4.27 PCI2 init 4.27 PCI2 reset 4.71 PCIe scan 00001de4:00000001 4.72 RP1_CHIP_INFO 20001927 4.75 RPi: BOOTLOADER release VERSION:4b019946 DATE: 2024/11/12 TIME: 16:10:44 4.82 BOOTMODE: 0x06 partition 0 build-ts BUILD_TIMESTAMP=1731427844 serial d04bb938 boardrev c04170 stc 4182099 4.92 AON_RESET: 00000003 PM_RSTS 00001000 4.96 PCIEx1: PWR 0 DET_WAKE 0 4.98 M.2 PCIe HAT not detected. 4.24 usb_pd_init status 1 4.28 XHCI-STOP 4.28 xHC0 ver: 272 HCS: 03000440 140000f1 07ff000a HCC: 0240fe6d 4.33 USBSTS 1 4.35 xHC0 ver: 272 HCS: 03000440 140000f1 07ff000a HCC: 0240fe6d 4.40 xHC0 ports 3 slots 64 intrs 4 4.52 XHCI-STOP 4.52 xHC1 ver: 272 HCS: 03000440 140000f1 07ff000a HCC: 0240fe6d 4.57 USBSTS 1 4.59 xHC1 ver: 272 HCS: 03000440 140000f1 07ff000a HCC: 0240fe6d 4.64 xHC1 ports 3 slots 64 intrs 4 4.72 Boot mode: SD (01) order f4 4.86 SD HOST: 200000000 CTL0: 0x00800000 BUS: 400000 Hz actual: 390625 HZ div: 512 (256) status: 0x1fff0000 delay: 276 4.97 SD HOST: 200000000 CTL0: 0x00800f00 BUS: 400000 Hz actual: 390625 HZ div: 512 (256) status: 0x1fff0000 delay: 276 4.62 OCR c0ff8000 [89] CID: 002750485344333247600000081e0157 CSD: 400e00325b590000e6e37f800a400000 4.70 SD: bus-width: 4 spec: 2 SCR: 0x02858082 0x00000000 4.78 SD HOST: 200000000 CTL0: 0x00800f04 BUS: 50000000 Hz actual: 50000000 HZ div: 4 (2) status: 0x1fff0000 delay: 2 4.87 MBR: 0x00002000, 1048576 type: 0x0c 4.89 MBR: 0x00102000,59469824 type: 0x83 4.93 MBR: 0x00000000, 0 type: 0x00 4.97 MBR: 0x00000000, 0 type: 0x00 4.01 Trying partition: 0 4.04 type: 32 lba: 8192 'mkfs.fat' ' bootfs ' clusters 261116 (4) 4.10 rsc 32 fat-sectors 2040 root dir cluster 2 sectors 0 entries 0 4.16 FAT32 clusters 261116 4.24 [sdcard] autoboot.txt not found 4.24 Select partition rsts 0 C(boot_partition) 0 EEPROM config 0 result 0 4.31 Trying partition: 0 4.34 type: 32 lba: 8192 'mkfs.fat' ' bootfs ' clusters 261115 (4) 4.40 rsc 32 fat-sectors 2040 root dir cluster 2 sectors 0 entries 0 4.46 FAT32 clusters 261115 4.52 Read config.txt bytes 190 hnd 0x4 4.54 [sdcard] pieeprom.upd not found 4.56 usb_max_current_enable default 0 max-current 900 4.68 Read bcm2712-rpi-5-b.dtb bytes 81451 hnd 0x50f7 4.70 dt-match: compatible: raspberrypi,5-model-b match: brcm,bcm2712 4.77 dt-match: compatible: brcm,bcm2712 match: brcm,bcm2712 4.83 Selecting USB low current limit 4.90 Read /config.txt bytes 190 hnd 0x4 4.94 Read /config.txt bytes 190 hnd 0x4 4.99 MESS:00:00:04.999071:0: Initial voltage 800000 temp 22442 5.99 MESS:00:00:05.199641:0: avs_2712: AVS pred 8948 894800 temp 21892 5.03 MESS:00:00:05.203248:0: vpred 894 mV +0 5.11 MESS:00:00:05.211880:0: FB framebuffer_swap 1 5.31 MESS:00:00:05.231715:0: Select resolution HDMI0/2 hotplug 0 max_mode 2 5.35 MESS:00:00:05.235766:0: Select resolution HDMI1/2 hotplug 0 max_mode 2 5.51 MESS:00:00:05.251255:0: dtb_file 'bcm2712-rpi-5-b.dtb' 5.53 Loading 'bcm2712-rpi-5-b.dtb' to 0x00000000 offset 0x100 5.66 Read bcm2712-rpi-5-b.dtb bytes 81451 hnd 0x50f7 5.08 Read /overlays/overlay_map.dtb bytes 5451 hnd 0x5297 5.39 PCIEx1: PWR 0 DET_WAKE 0 5.52 Read /config.txt bytes 190 hnd 0x4 5.34 Read /cmdline.txt bytes 177 hnd 0x21d 5.53 BMD "armstub8-2712.bin" not found 5.54 fs_open: 'armstub8-2712.bin' 5.57 Loading 'zephyr.bin' to 0x00000000 offset 0x200000 5.00 Read zephyr.bin bytes 74184 hnd 0x5 5.01 PCI1 reset 5.13 PCI2 reset 5.23 USB-OTG disconnect 5.62 MESS:00:00:05.762870:0: Starting OS 5762 ms 5.68 MESS:00:00:05.768385:0: 00000040: -> 00000480 5.70 MESS:00:00:05.770239:0: 00000030: -> 00100080 5.74 MESS:00:00:05.774952:0: 00000034: -> 00100080 5.79 MESS:00:00:05.779665:0: 00000038: -> 00100080 5.84 MESS:00:00:05.784378:0: 0000003c: -> 00100080 NOTICE: BL31: v2.6(release):v2.6-240-gfc45bc492-dirty NOTICE: BL31: Built : 13:41:55, Sep 23 2024 *** Booting Zephyr OS build v4.3.0-3034-g2062a21ed267 *** thread.yield.preemptive.ctx.k_to_k - Context switch via k_yield : 2 cycles , 47 ns : thread.yield.cooperative.ctx.k_to_k - Context switch via k_yield : 2 cycles , 46 ns : isr.resume.interrupted.thread.kernel - Return from ISR to interrupted thread : 2 cycles , 38 ns : isr.resume.different.thread.kernel - Return from ISR to another thread : 1 cycles , 32 ns : thread.create.kernel.from.kernel - Create thread : 25 cycles , 480 ns : thread.start.kernel.from.kernel - Start thread : 5 cycles , 94 ns : thread.suspend.kernel.from.kernel - Suspend thread : 2 cycles , 40 ns : thread.resume.kernel.from.kernel - Resume thread : 2 cycles , 42 ns : thread.abort.kernel.from.kernel - Abort thread : 0 cycles , 17 ns : fifo.put.immediate.kernel - Add data to FIFO (no ctx switch) : 0 cycles , 2 ns : fifo.get.immediate.kernel - Get data from FIFO (no ctx switch) : 0 cycles , 1 ns : fifo.put.alloc.immediate.kernel - Allocate to add data to FIFO (no ctx switch) : 2 cycles , 50 ns : fifo.get.free.immediate.kernel - Free when getting data from FIFO (no ctx switch) : 2 cycles , 45 ns : fifo.get.blocking.k_to_k - Get data from FIFO (w/ ctx switch) : 3 cycles , 68 ns : fifo.put.wake+ctx.k_to_k - Add data to FIFO (w/ ctx switch) : 5 cycles , 95 ns : fifo.get.free.blocking.k_to_k - Free when getting data from FIFO (w/ ctx switch) : 3 cycles , 68 ns : fifo.put.alloc.wake+ctx.k_to_k - Allocate to add data to FIFO (w/ ctx switch) : 5 cycles , 98 ns : lifo.put.immediate.kernel - Add data to LIFO (no ctx switch) : 0 cycles , 1 ns : lifo.get.immediate.kernel - Get data from LIFO (no ctx switch) : 0 cycles , 1 ns : lifo.put.alloc.immediate.kernel - Allocate to add data to LIFO (no ctx switch) : 2 cycles , 48 ns : lifo.get.free.immediate.kernel - Free when getting data from LIFO (no ctx switch) : 2 cycles , 44 ns : lifo.get.blocking.k_to_k - Get data from LIFO (w/ ctx switch) : 3 cycles , 68 ns : lifo.put.wake+ctx.k_to_k - Add data to LIFO (w/ ctx switch) : 4 cycles , 84 ns : lifo.get.free.blocking.k_to_k - Free when getting data from LIFO (w/ ctx switch) : 3 cycles , 69 ns : lifo.put.alloc.wake+ctx.k_to_k - Allocate to add data to LIFO (w/ ctx switch) : 4 cycles , 83 ns : events.post.immediate.kernel - Post events (nothing wakes) : 0 cycles , 16 ns : events.set.immediate.kernel - Set events (nothing wakes) : 0 cycles , 16 ns : events.wait.immediate.kernel - Wait for any events (no ctx switch) : 0 cycles , 6 ns : events.wait_all.immediate.kernel - Wait for all events (no ctx switch) : 0 cycles , 7 ns : events.wait.blocking.k_to_k - Wait for any events (w/ ctx switch) : 2 cycles , 54 ns : events.set.wake+ctx.k_to_k - Set events (w/ ctx switch) : 4 cycles , 81 ns : events.wait_all.blocking.k_to_k - Wait for all events (w/ ctx switch) : 3 cycles , 70 ns : events.post.wake+ctx.k_to_k - Post events (w/ ctx switch) : 5 cycles , 97 ns : semaphore.give.immediate.kernel - Give a semaphore (no waiters) : 0 cycles , 6 ns : semaphore.take.immediate.kernel - Take a semaphore (no blocking) : 0 cycles , 6 ns : semaphore.take.blocking.k_to_k - Take a semaphore (context switch) : 2 cycles , 51 ns : semaphore.give.wake+ctx.k_to_k - Give a semaphore (context switch) : 3 cycles , 60 ns : condvar.wait.blocking.k_to_k - Wait for a condvar (context switch) : 3 cycles , 72 ns : condvar.signal.wake+ctx.k_to_k - Signal a condvar (context switch) : 4 cycles , 86 ns : stack.push.immediate.kernel - Add data to k_stack (no ctx switch) : 0 cycles , 0 ns : stack.pop.immediate.kernel - Get data from k_stack (no ctx switch) : 0 cycles , 0 ns : stack.pop.blocking.k_to_k - Get data from k_stack (w/ ctx switch) : 3 cycles , 70 ns : stack.push.wake+ctx.k_to_k - Add data to k_stack (w/ ctx switch) : 4 cycles , 76 ns : mutex.lock.immediate.recursive.kernel - Lock a mutex : 0 cycles , 7 ns : mutex.unlock.immediate.recursive.kernel - Unlock a mutex : 0 cycles , 3 ns : heap.malloc.immediate - Average time for heap malloc : 1 cycles , 35 ns : heap.free.immediate - Average time for heap free : 2 cycles , 37 ns : =================================================================== PROJECT EXECUTION SUCCESSFUL |

まとめ

ラズパイ5のUARTのコネクタケーブルを作ってみました。

本来はラズパイの専用デバッグケーブルに付属してくるものです。

JSTのSHの3ピンですが、コネクタを自作して対応してみました。

もしラズパイ5のUARTケーブル必要になりましたら、試してみてください。

コメント