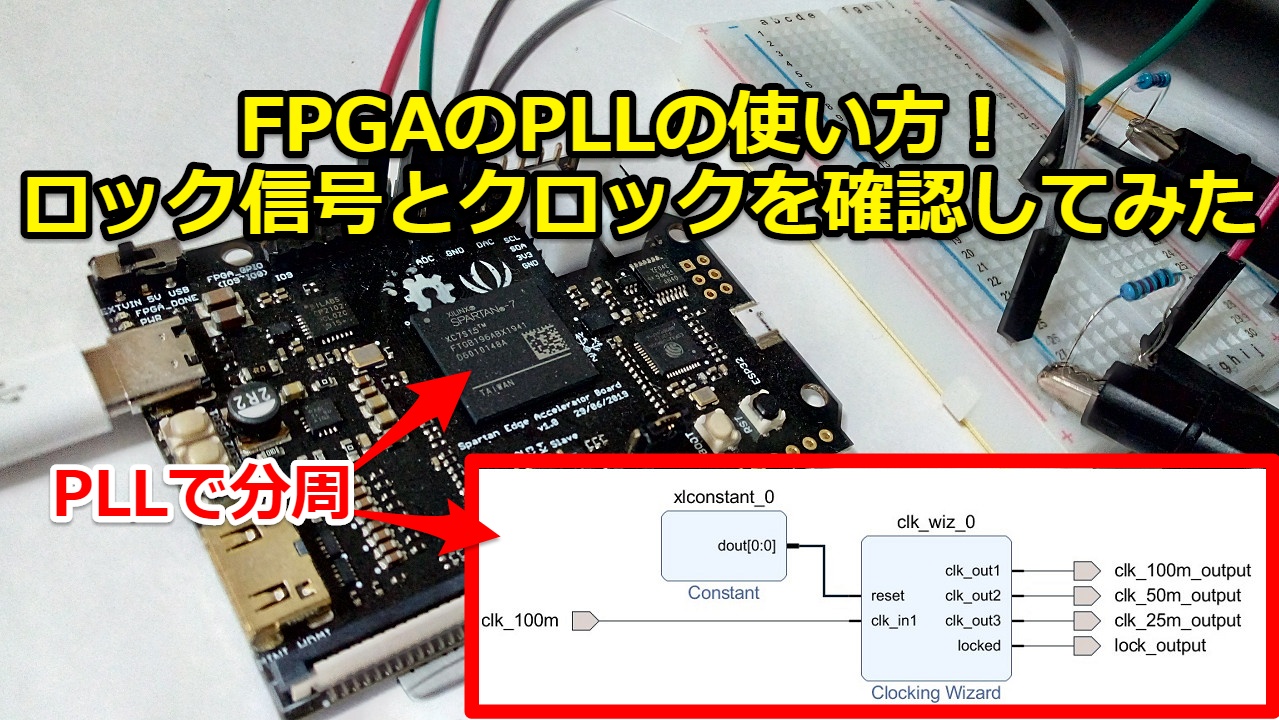

FPGAのPLLを使えば任意の周波数のクロックが出力可能です。

実際に分周したクロックをロック信号と一緒にオシロスコープで確認してみました。

PLLのIPの設定方法からFPGAのピン設定まで分かりやすく紹介します。

FPGAのPLLの使い方!ロック信号と一緒にクロック出力してみた

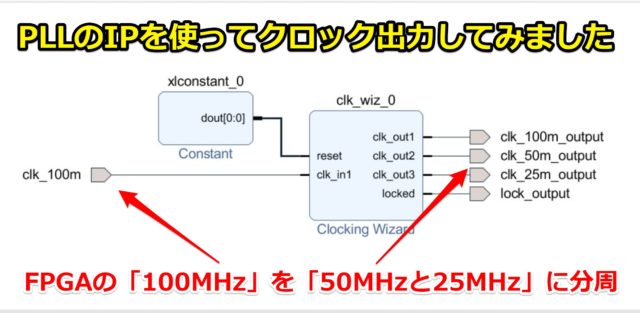

XilinxのFPGAを使い、PLLのIPを使ってクロック出力してみました。

FPGA評価ボード内部の100MHzを50MHzと25MHzに分周しています。

実際にFPGAからのクロック出力をオシロスコープで確認しています。

またコンフィグレーションからPLLロック信号が出力するまでの波形を測定しています。

PLLからクロック出力するまでの一連の流れが分かります。

FPGAのPLLの簡単な使い方を一から紹介していきます。

動画でもオシロスコープでの測定の様子含めて説明しています。是非一緒にご覧ください。

XilinxのFPGAでPLLの使い方

今回使用するFPGAはXilinxのSpartan7です。

XilinxのPLLのIPを使用してシステムクロックの100MHzを50MHzと25MHzに分周します。

今回使用しているFPGAの評価ボードは下記記事で紹介しています。(リンク先はこちら)

開発環境のインストール方法・プロジェクトの作り方含めて解説しています。

今回紹介するのはあくまで個人のテストレベルの設計ということをご了承ください。

シミュレーションなどの手順を省略しています。

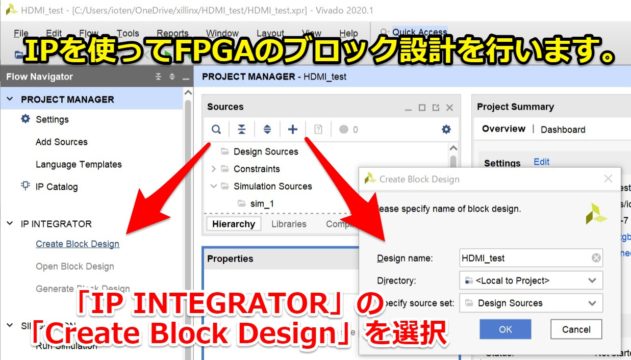

プロジェクトを作りましたら、「IP INTEGRATOR」→「Create Block Design」を選択します。

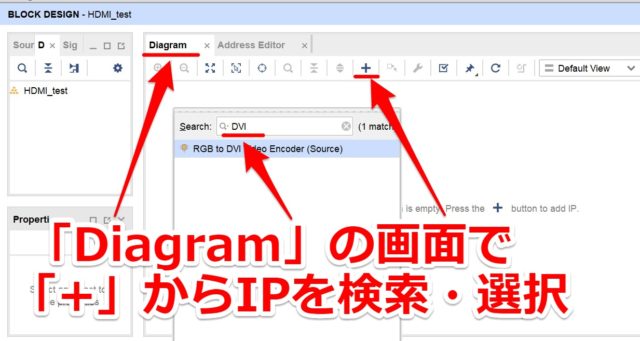

「Diagram」の画面が出たら「+」をクリックするとIPを検索・選択できます。

これで自由にブロック設計を進めていけます。

Clocking Wizardを使用する

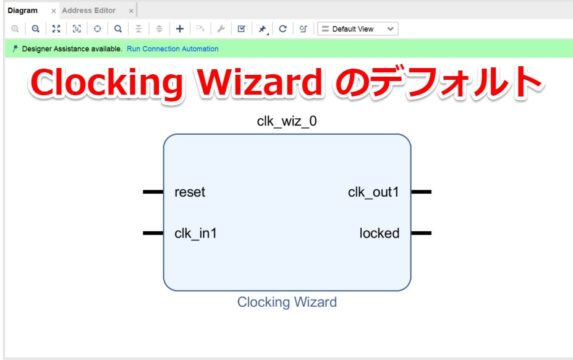

XilinxのPLL(MMCM)のIPは「Clocking Wizard」を使います。

開発環境のVivadoにデフォルトで入っており、IPの検索で「Clock」と入力すれば出てきます。

デフォルトだとPLLでのクロック入出力の他にリセット入力とロック出力があります。

今回は基本的にデフォルト設定で対応しています。

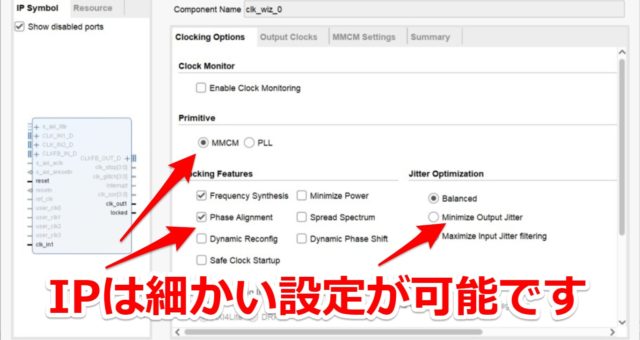

IPをダブルクリックすると細かい(位相・ジッタなどの)設定が可能です。

本来はMMCMとPLLの違いなどもありますが、今回は省略します。

(どちらでも分周・逓倍が可能です。MMCMの方が高機能のイメージです。)

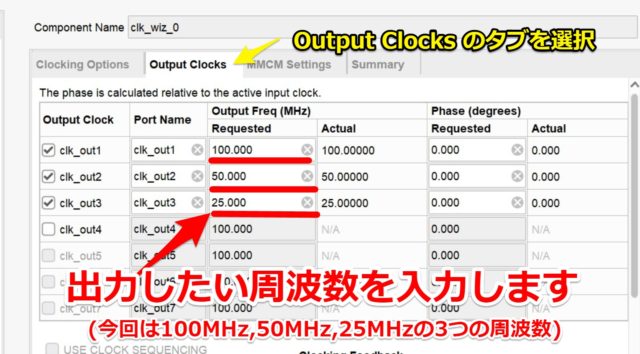

出力する周波数を設定するため「Output Clocks」のタブを選択します。

出力したい周波数を入力していきます。

今回のテストでは一つのPLLから100MHz,50MHz,25MHzの3つの周波数を出力しています。

入力ポートにクロック100MHzを設定

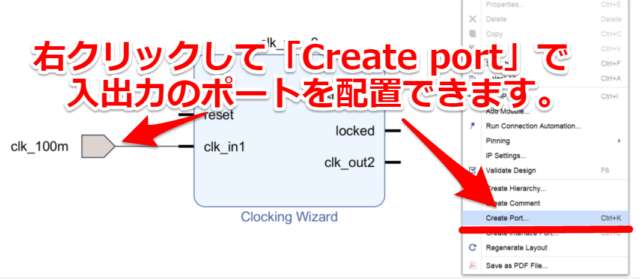

「Diagram」の箇所で右クリックすると「Create port」で入出力のポートを配置できます。

今回の入力ポートはFPGA評価ボードのクロック100MHzを使います。

Typeを「Clock」にしてFrequencyを「100」MHzにしときました。

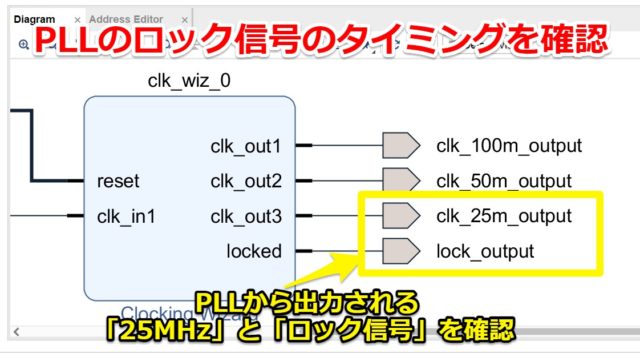

出力ポートはロック信号含めて設定

出力も同様にポートを作成してPLLに接続していきます。

Create Portの設定箇所のDirectionを「Output」にすれば出力ポートとなります。

今回はPLLのロック信号含めて設定しました。

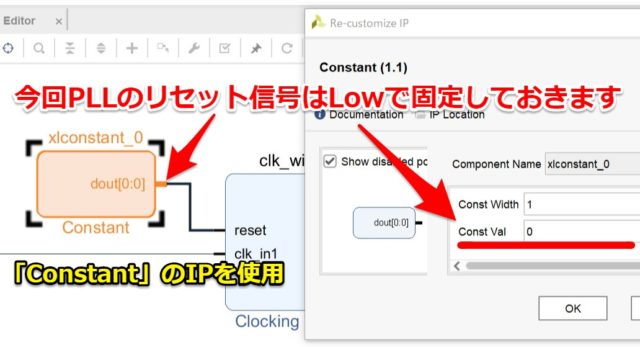

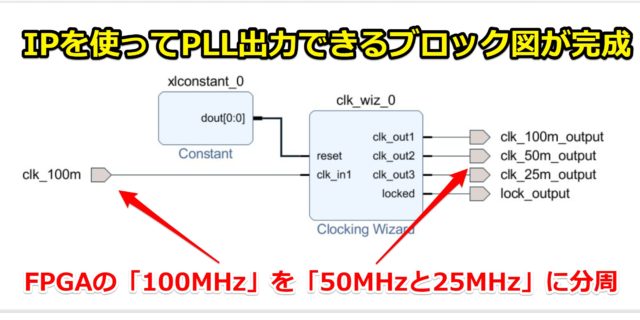

PLLのリセット信号はLowで固定しておく

今回PLLのリセット信号はLowで固定して、常に動作するようにしておきます。

「Constant」のIPを使用すれば定数(Low/Hi)を設定できます。

Const Valを「0」のLowとしておきます。

IPブロック図をコンパイルするための準備

これまでの操作でIPを使ってFPGAでPLL出力できるブロック図が完成できました。

IPコア間を配線すると下記のような形になるはずです。

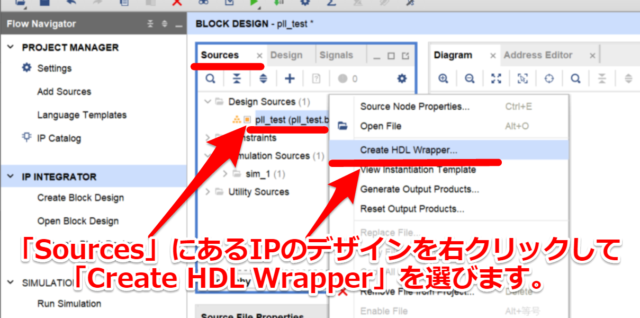

最終的にコンパイルできるように一度IPブロック図の上位層を作成します。

「Sources」にあるIPブロックを右クリックして「Create HDL Wrapper」を選びます。

おそらく選択子が出てきますが「OK」を進めていけば大丈夫です。

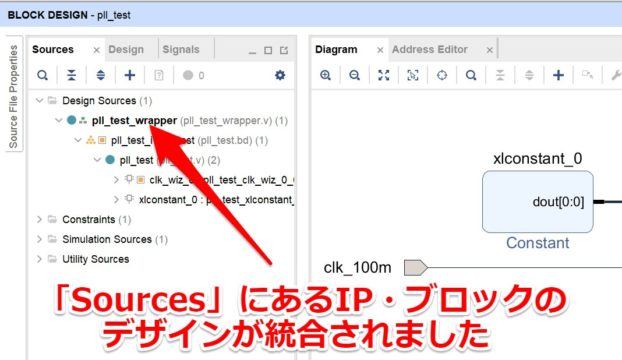

「Sources」にあるIP・ブロックのデザインが無事統合されました。

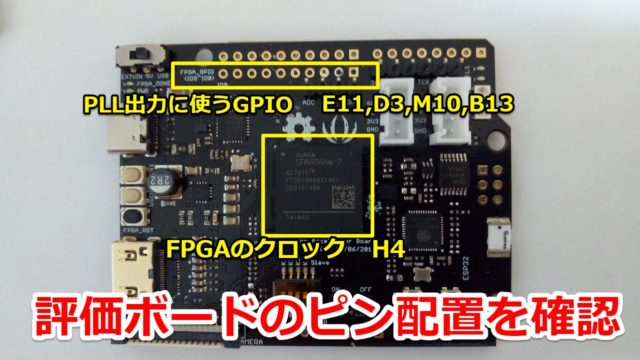

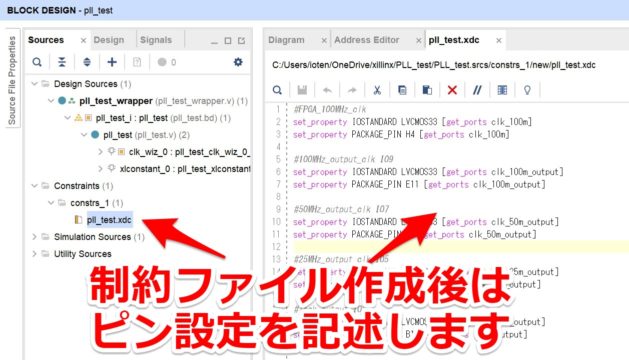

評価ボードに合わせたピン設定を行う

最後に評価ボードで使うFPGAのピン配置を設定していきます。

入力100MHzのクロック、出力のGPIOのピンを選択します。

ピン配置に関しては各個人で使うFPGAの評価ボードの回路図を参照お願いします。

FPGAのピン設定の制約ファイル

FPGAで使うピンを制約ファイル(.xdc)で記述したのが下記となります。

(制約ファイルの書き方も色々あると思いますので、この記述もあくまで一例です。)

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 |

#FPGA_100MHz_clk set_property IOSTANDARD LVCMOS33 [get_ports clk_100m] set_property PACKAGE_PIN H4 [get_ports clk_100m] #100MHz_output_clk IO9 set_property IOSTANDARD LVCMOS33 [get_ports clk_100m_output] set_property PACKAGE_PIN E11 [get_ports clk_100m_output] #50MHz_output_clk IO7 set_property IOSTANDARD LVCMOS33 [get_ports clk_50m_output] set_property PACKAGE_PIN D3 [get_ports clk_50m_output] #25MHz_output_clk IO5 set_property IOSTANDARD LVCMOS33 [get_ports clk_25m_output] set_property PACKAGE_PIN M10 [get_ports clk_25m_output] #lock_output IO3 set_property IOSTANDARD LVCMOS33 [get_ports lock_output] set_property PACKAGE_PIN B13 [get_ports lock_output] |

制約ファイルの入れ方に関しては下記記事で別例を紹介しています。

今回はシングルエンドのクロックですが、HDMIのような差動クロックも定義できます。

よろしければ一緒にご覧ください。(リンク先はこちら)

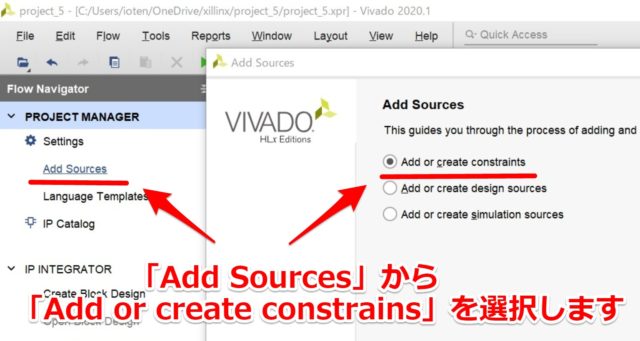

制約ファイルをソースに追加する

「Add Sources」から「Add or create constrains」を選択します。

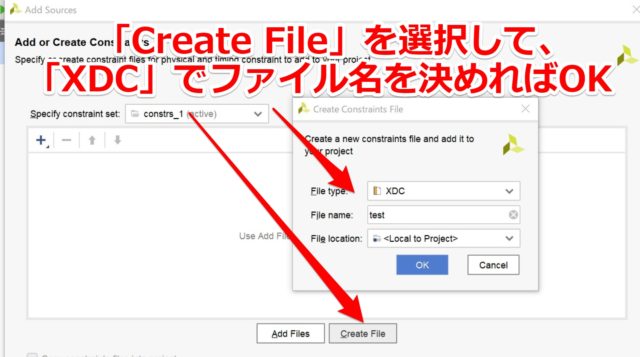

「Create File」を選択して、デフォルトの「XDC」でファイル名を決めればOKです。

作成後は先述した制約ファイルを参考に記述してもらえれば完成です。

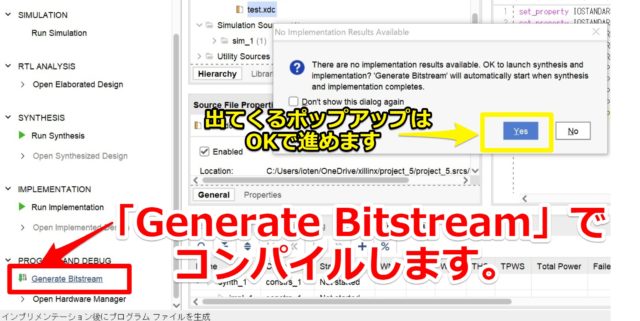

コンパイルしてFPGAに書き込む用意をします

あとは「Generate Bitstream」でコンパイルして成功するか確認します。

ポップアップが出ますが気にせずOKを押して進めます。

コンパイルが上手くいきましたら、FPGAに書き込む用意を行います。

書き込む方法は各評価ボードで異なりますので、各評価ボードの手順に従ってください。

今回の評価ボードは「JTAGケーブル」もしくは「USB(とSDカード)経由」で書き込めます。

JTAG-USBケーブルを使った書き込み方法は下記で紹介しています。(リンク先はこちら)

特殊ですが「USB(とSDカード)」経由の書き込み方法を確認したい方は下記を参考ください。

今回のテスト動画で実施しているのはこちらの手段です。

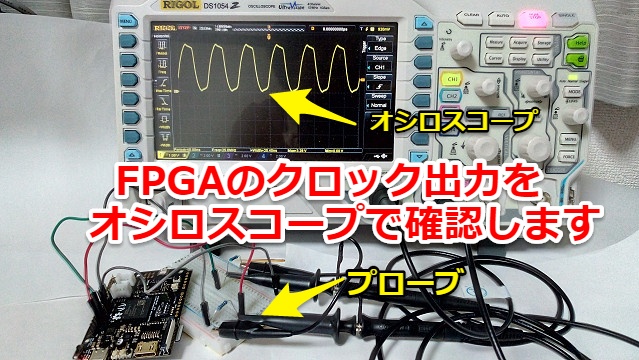

FPGAのクロック出力をオシロスコープで確認する

FPGAの準備はできましたので、クロックを確認できる環境を用意します。

オシロスコープとプローブをFPGAに接続します。

GPIOとGND間にジャンパーを飛ばして10kΩ抵抗を接続しています。単純な回路です。

クロック出力とロック信号の両方とも同じ回路構成です。

※本来はFPGAのピンに直近で測定するのがベストですが、プローブが掴めなかったためです。

PLLで50MHzに分周した波形

実際に50MHzを測定した波形が下記です。周波数としては50MHzを確認できました。

しかし波形がSin波のように正弦波のように見えるのはオシロのスペック不足です。

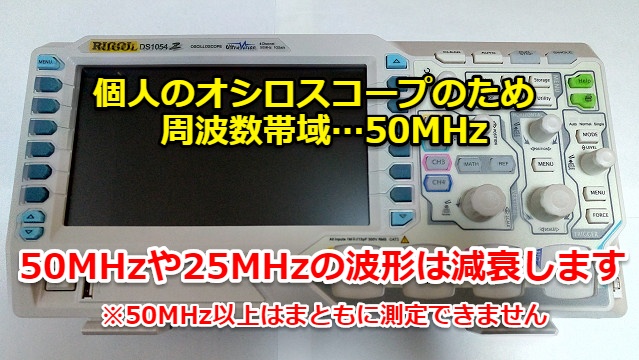

今回のような波形になっている理由はオシロスコープの周波数帯域が個人用のためです。

周波数帯域が50MHzのオシロのため、50MHzの波形は正確に測定出来ません。

FPGAからは方形波の形で出力されていますが減衰されて正弦波のように見えています。

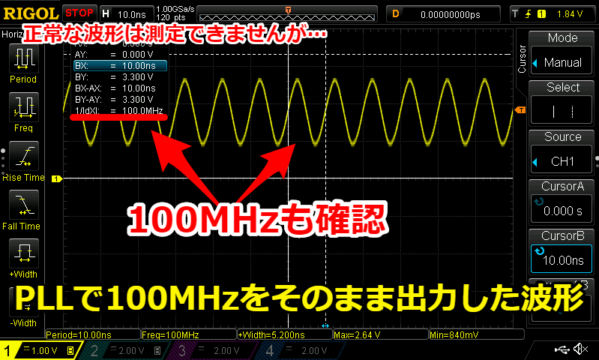

PLLで100MHzをそのまま出力した波形

ちなみにこのオシロで100MHzのクロックを測定もしてみました。

(もちろん減衰されて)正常な波形は測定出来ず、電圧レベルの3.3Vが確認できませんでした。

一応、100MHzの周波数は確認できました。

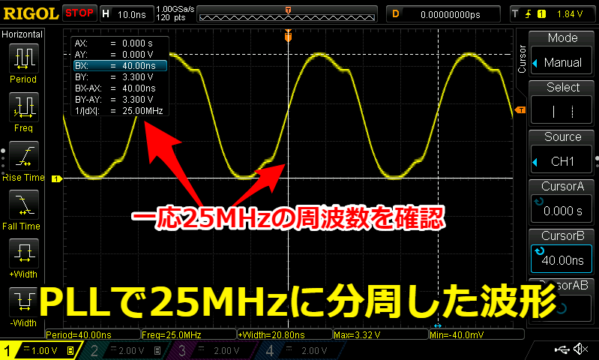

PLLで25MHzに分周した波形

25MHzでも結構怪しいですが、方形波の形に近づいてきています。

PLLから25MHzから出力されていることを確認できました。

今回波形が汚い理由の一つとして測定位置(ジャンパー先で測定)が悪いです。

FPGAのピン近くで測定すればもう少し改善されたと思います。

FPGAのPLLのロック信号のタイミングを確認する

今回はPLLから出力されているロック信号をクロックと一緒に確認してみます。

PLLから25MHzが安定してから出力されますが、ロック信号との関係を見てみます。

オシロスコープのCH1で25MHz、CH2でロック信号を確認します。

ロック信号をトリガーにしてPLLが動作してからの一連の波形を測定します。

冒頭でも紹介しましたが、実際に測定した動画が下記になります。

FPGA起動→コンフィグレーション→ロック信号出力の流れが分かりやすいと思います。

是非一緒にご覧ください。

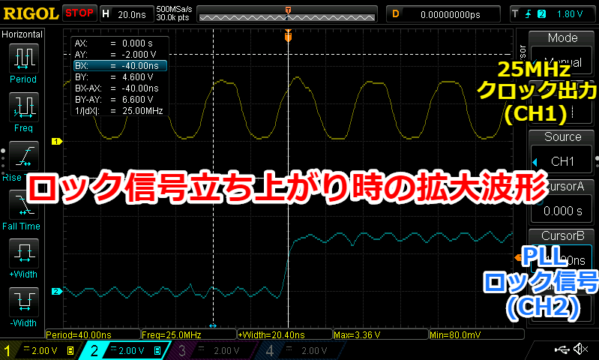

コンフィグレーションからPLLがロックするまでの波形

あくまで一例となりますが、実際に測定した結果が下記となります。

「黄色の波形がCH1でPLL出力の25MHz」、「青色の波形がCH2でロック信号」です。

コンフィグレーション後はピン設定され、その後PLL起動するまでに約10usほどかかっています。

そしてPLL起動してPLLロック信号が出力するまでに約13usほどでした。

※コンフィグレーション…FPGAへのプログラム書き込み

コンフィグレーション前(FPGA起動直後)は内部PUの影響で電圧値が約中間となっています。

(おそらく内部PUが約10kΩ、今回の外付け抵抗が10kΩのため1:1分圧されて中間値の様子)

ロック信号立ち上がり時を拡大すると下記波形となりました。PLL出力が出来ています。

その後はPLL出力・ロック信号がHi(1)状態を維持します。

まとめ

今回はFPGAのPLLの使い方に関して紹介させていただきました。

記事をまとめますと下記になります。

次回の記事では今回作成した25MHzを使ってACカップリングの波形を確認しています。

FPGAやCPUなどで高速信号を取り扱う上でACカップリングは重要な回路です。

実際の測定例含めて分かりやすく紹介しています。(リンク先はこちら)

コメント